ハイエンドのBulldozerコアを用いる新プロセサ群

Bulldozerは、AMDの新開発の高性能で電力効率も高いハイエンド用のプロセサモジュールである。Bulldozerコアを使う最初の製品はZambeziというコード名の8コアのデスクトップ用のプロセサであり、これはこの夏にも発売されると予想される。それに続いて、1~2チップ構成の小規模サーバ用のValencia、 4チップ構成が可能なInterlagosが計画されている。なお、Interlagosは2個のチップをマルチチップパッケージに搭載しており、16コアとなっている。

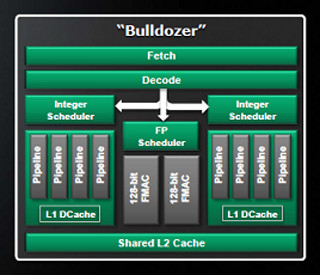

Bulldozerの設計の大きな特徴は、通常のプロセサの2コアをまとめて1つのモジュールとし、命令の読み出し(Fetch)とデコード(Decode)部分や2次キャッシュは2コアで共用する設計となっている点である。また、浮動小数点ユニットも2コアで共用されている。一方、使用頻度の高い整数命令の処理部や1次データキャッシュは個別に持っている。このような設計とすることにより、性能的には通常の2コアと殆ど変らないが、コアあたりのチップ面積は減少し、消費電力的にも低減できて性能/電力を改善できるというメリットがある。

そして、このBulldozerモジュールを4個搭載するZambeziチップのフロアプランは次の図のようになっている。

Bulldozerモジュールと2MBの2次キャッシュのペアが2個ずつ上下に配置され、中央部分には全体で8MBの共有3次キャッシュとメモリやI/Oインタフェースを接続するノースブリッジが配置されている。そして、右辺にはDDR3メモリのインタフェース、左辺と上下の辺の左側にはHyperTransportのインタフェース回路が配置されている。

チップ全体のブロックダイヤグラムは次の図のようになっており、System Requestキューとクロスバを中心として、上側に4つのBulldozerモジュール、左に8MBの3次キャッシュ、右に2チャネルのDDR3インタフェース、下側に4本のHyperTransportという構成になっている。

キャッシュの動作についてはあまり明確に述べられなかったが、現在のOpteronと同じで、メモリから読まれたでデータは直接2次キャッシュに送られ、3次キャッシュは2次キャッシュを追い出されたキャッシュラインを格納するビクティムキャッシュになっていると思われる。そして、キャッシュコヒーレンシの維持に関しては、各チップのメモリコントローラが自分の受け持ちのメモリのコヒーレンシに責任を持つとのことであり、ホームノードがスヌープを送る方式と思われる。

また、3次キャッシュの一部をスヌープフィルタとして使い、コヒーレンシトラフィックを減らすという機能も引き続き実装されている。

消費電力を低減させるための電力制御機構は電圧可変のコア用の電源とコアごとのパワーゲートという構造になっている。そして、消費電力枠に余裕がある場合は全コアのクロックと電源電圧を引き上げる全コアターボと、半分のコアがパワーゲート状態の場合は動作中の半分のコアのクロックと電源をさらに引き上げるMaxターボというモードを持っている。

これらのターボにより、どの程度、クロックを上げることができるかについては明らかにされなかったが、この図の棒グラフでは、全コアターボで30%程度、Maxターボでは60%程度クロックアップとなっている。しかし、この図がそこまで精度を意図して書かれているかどうかは分からない。

製品としては、940ピンのAM3+ソケットを使うデスクトップ用のZambezi、1207ピンのC32ソケットを使う小規模サーバ用のValencia、1944ピンのG34ソケットを使うハイエンドサーバ用のInterlagosが出る予定である。

ZambeziはBulldozerモジュールを4個搭載する8コアのマルチプロセサであり、2チャネルのアンバッファードのDDR3-1866インタフェースを持っている。外部接続に関しては、4本のHyperTransportのうちの1本だけを使い(残りの3本は未接続)、ここにAMDシリーズ9チップセットを接続し、PCIExpressなどを引き出す。ZambeziはHyperTransportが1本であり、1つCPUチップを接続する用途に限定されたハイエンドデスクトップシステム用プロセサである。

Valenciaもほぼ同じであるが、HyperTransportが2本となっており、2チップを接続する構成が可能となっている。メモリインタフェースはDDR3-1600とZambeziより少し遅くなっているが、RDIMMやLRDIMMをサポートしDIMMの接続枚数を増やし、サーバ向けに大容量のメモリをサポートできるようになっている。

ハイエンドのInterlagosは2つのチップを1つのパッケージに搭載し、両者の間をHyperTransportで繋いだ構造になっている。このため、パッケージ単位でみると16コアプロセサで3次キャッシュも16MBということになる。そして、メモリチャネルはDDR3-1600が合計4本となる。

HyperTransportは、左のマスターチップからはフル幅の16ビット幅のものが2本と8ビットの半幅のものが1本、右のスレーブチップからはフル幅と半幅が各1本引き出されており、全体ではフル幅3本、半幅2本となっている。

次の図に示すように、4個のInterlagosチップをフル幅のHyperTransportで直接接続し、下側の2個からは半幅のHyperTransportでブリッジチップを接続したシステムを構成できる。この構成では、64コア、メモリはDDR3チャネルが16本という大規模なシステムが構成できる。