Memory関連

案外に話がなかったのがMemory関連である。Sandy Bridgeに直接関連した部分では話題は皆無。IDFのTrack全体を見渡しても、(GOLD SponserになっているSamsungとRambusのセッション以外は)"Where Is Memory Going for Your Platform"というQ&Aセッションで多少触れられている程度だ。とは言え、ここである程度方向性は見えてきたのでちょっとご紹介したい。

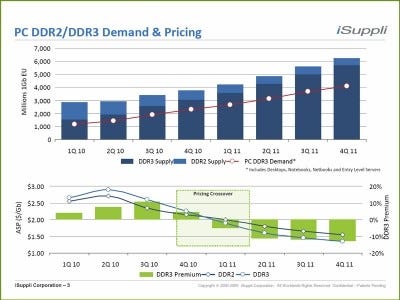

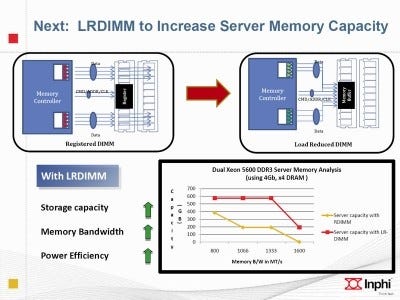

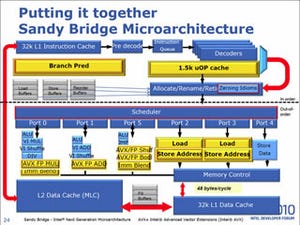

Sandy Bridgeの世代も引き続きDDR3メモリが主流になるのは間違いない。このセッションにおけるiSuppliのデータによれば、今年中に完全にDDR3のプレミアはなくなるとしており(Photo08)、このまま引き続きDDR3がメインのまま行くことになる。ただ、今のDDR3の場合はデスクトップにはいいが、サーバ用途では容量の点で若干不足気味である。これをカバーするために、LRDIMMのサポートをすることを計画している(Photo09)。既存のRegistered DIMMではCMD/Address/Clockの各信号線のデータを、チップ上のBuffer(Register)を介することで安定動作を図るというものだが、データ線そのものはカバーされなかった。LRDIMMではこのデータ線にもRegisterを配することで、高速動作時でも安定して動作できるようにするというものだ。要するにDDR3の場合、信号速度が速すぎて複数モジュールを搭載すると伝送に支障が出るため、枚数を減らすか(これは容量が不足する)、スピードを落とすか(これは帯域に支障が出る)になる。これを若干緩和するための方策がLRDIMMである。600GB、というあたりは恐らく4RankのDIMMとかを想定しているものと思われる。

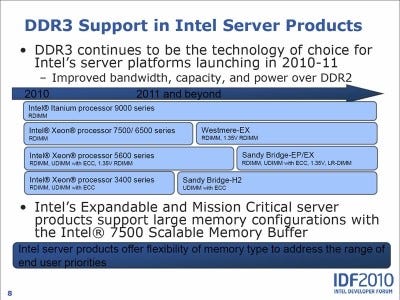

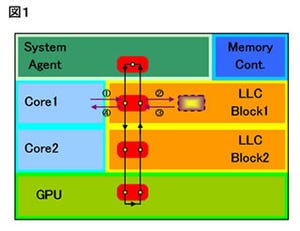

これがサポートされるのは、Sandy Bridge-EP/EX、つまり現在のXeon 5600シリーズの後継製品(Photo10)ということなので、Sandy Bridgeそのものにはこの機能は入るようだ。ただ現在のXeon 3400の後継となるSandy Bridge-H2はUDIMM with ECCということなので、ローエンド向けにはこの機能を殺すか、もしくは統合しないのであろう。

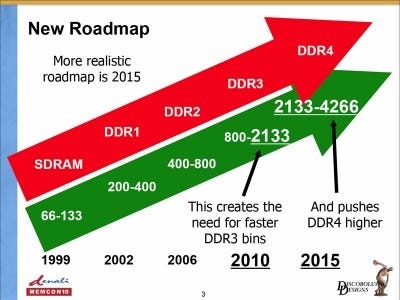

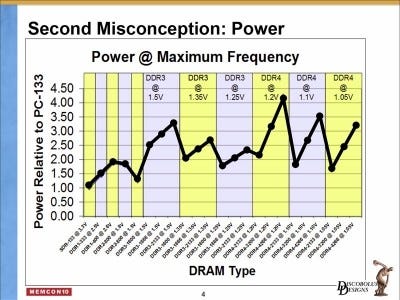

さて、問題はこの世代がどこまでのDDR3をサポートするか、である。実はDDR4のロードマップが一度完全崩壊して、再度検討しなおしになっているのだが、これに先立ちDDR3の延命工作が行われている。Photo10にもちらっと出ているが、既に1.35V動作のDDR3は標準化が行われており、メーカーからもサンプルが出てきている状況である。これに加えてDDR3に関しては最大2133MHzまでが視野に入っており、DDR4はこの次である(Photo11)。スピードのみならず電圧もこの先は1.25Vが射程に入っている事が判る。一応スペック的には1.5V動作でDDR3-2133まで登場するが、こちらは消費電力が大幅に増える。なので、DDR3-1866/2133に関しては1.35V動作品から入り、本命は1.25V世代ではないかといわれている。今のところこの1.25V品が出てくるのは2012年以降(メモリベンダーのプロセスの微細化次第なところであるが、量産出荷は2013年? あたりと見られている)なので、これはIvy Bridgeでは考慮する必要があるが、Sandy Bridgeではサポートしないだろう。ただPhoto10にもあるように1.35V動作はサポートするようなので、可能性としてはDDR3-1866/2133がサポートされる余地はある事になる。個人的な予測としては、SandyBridge-EPでは恐らく入らないだろうが、Sandy Bridge-H2では入りそうな気がする。このあたりがどうなるか、ちょっと製品が楽しみなところだ。