CPUパッケージ

既報の通り、AMDは3月29日にMagni-Coursのコード名で知られていた8コア/12コアのOpteron 6000シリーズを発表した(Photo01)。

|

Photo01: Opteron 6000シリーズのPackageをもつJohn Fruehe氏(Director of Marketing for Server/Workstation Division)。ちなみに前職はDirector of Business Development,Server/Workstation Divisionなので少し職種が変わった(というか、昇格した)模様。 |

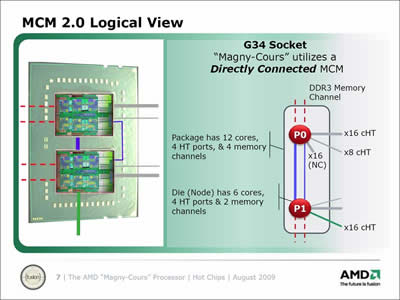

基本的にはOpteron 6000シリーズは既存のShanghaiないしIstanbulベースのQuad/Six-Core Opteronを2つ、MCMパッケージに封入した構造をとる。実はこの内部構造自体は、昨年8月に開催されていたHot Chips 21で公開されており(Photo02)、2つのShanghai/Istanbulが16x16と8x8という2レーンのHyperTransport Linkで接続されていることが明らかにされている。面白いのはこれが16x16を2本にしなかった事であるが、以前AMDのスタッフに非公式に聞いた話では、別に16x16を2本にしても帯域は増えない(32x32としては動作しないのだそうだ)からで、但し例えばメモリの転送を行いながら、更にCache Coherencyを保つためのSnoopを行う様なケースでは、8x8を別に用意しておくことで丁度Side Band Transferの様な動作が期待できるらしい。詳しいことは教えてもらえなかったが、察するに各コアに搭載されているXBarは、接続される帯域に応じてQoS的な動作が可能なようで、データ転送など帯域が必要な場合には16x16レーンを、それ以外には8x8レーンを使うという事のようだ。

|

Photo02: 昨年8月に行われたPat Conway氏による"Blade Computing with the AMD Opteron Processor (“Magny-Cours”)"のプレゼンテーションより。 |

ちなみに、大昔のプレゼンテーションによれば、理論上は4つの16x16レーンを8つの8x8レーンとして動作させることも出来る(少なくともHyperTransport 3.0にはその機能が追加されている)筈だ。実際今回も8x8レーンが混在しているあたり、これを伺わせる。となると、Magni-Coursは理論上、コアあたり16x16レーンを1.5レーン使っているから、外部に16x16レーンを2.5レーン出せるはずで、2コア合わせれば5レーン相当になる(か、16x16レーン×4+8x8レーン×2の構成かもしれない)が、流石にここまで出す必要はないと判断したのであろう。

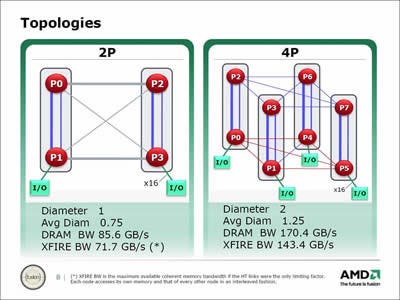

これによる効果は明確である。Photo03は説明会における資料で、あたかも全ダイが1hopで繋がっているように見えるが、実際はもう少し面倒である。Photo04もまたHot Chipsの資料だが、2Pの構成の場合、平均Hop数は(1+1+1+0)÷4=0.75となる。ここで言う「Hop数」というのは、「あるCPUコアがメモリをアクセスしようとした時に、そのメモリにたどり着くまでに必要なルーティング数」である。例えば2Pのケースで、P0上で動くプログラムがメモリアクセスをしようとしたときに、それがP0に繋がるコントローラの先のDIMMにおかれていれば、ペナルティは0である。ところがP1~P3に繋がるコントローラの先のDIMMだった場合、それぞれP0→P1/P2/P3にリクエストを出し、その結果が返ってくるのを待つ必要がある。厳密に言えば、P0→P1の場合、配線はMCM上で済むからルーティングのレイテンシは最短で済むが、P2/P3の場合にはマザーボード上の配線を経ることになり、若干レイテンシが増える事になるが、まぁこれはルータの処理に比べれば大きなものではないだろう。

これが4Pになるとどうなるか、というとやはりP0からリクエストを出した場合、平均Hop数は(0+1+1+1+1+2+2+2)÷8=1.25となる。P0自身ならば0だが、P1/P2/P4/P5の場合は1Hop、そしてP3/P6/P7の場合には2Hopとなるからだ。

もっともIstanbulまでの、つまりHyperTransport Linkが3本までの構成だと、このあたりのHop数が特に4P以上の場合にグンと増えるので(このあたりは以前こちらに書いた)、やはりHyperTransport Linkが1本増えたのは大きな効用だったといえる(端的に言えば、Photo03の"Direct Connect Architecture 2.0"というのは、要するにHyperTransport Linkを1本増やしたということである)。

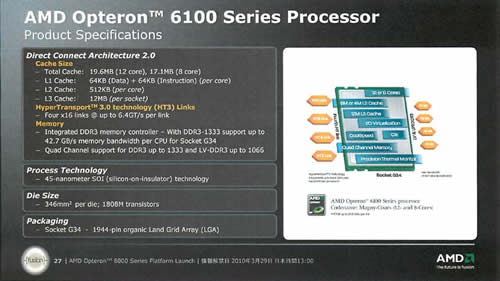

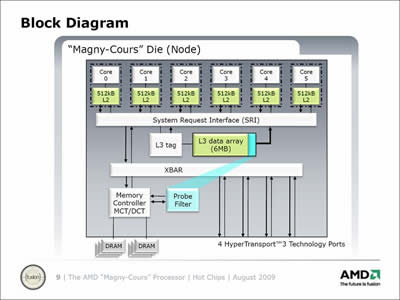

ちなみに各コアそのものについては、基本的にはIstanbul世代の設計をそのまま踏襲したとFruehe氏は説明する。厳密に言えば、IPCの若干の向上に繋がるような小改善は行ったというが、それは厳密に言えばShanghai/IstanbulベースのOpteronと比較しての事で、Desktop向けのPhenom II X4(や、まもなく登場するPhenom II X6)と同じものと思われる(Photo05)。パッケージはごらんの様に(Photo06,07)かなり横長のものとなったが、MCM構造をとる以上致し方ないだろう(Photo08)。

|

Photo05: ちなみにProbe FilterについてはIstanbulベースのSix-Core Opteronで既に実装されている。ただShanghaiベースのQuad-Core Opteronでは未実装(か、実装していても無効化)されているので、8コアのMagni-Coursに関しては初実装という事になる。 |

ところで本文では「Opteron 6000シリーズ」と書いたが、実際のCPUの型番は「Opteron 6100シリーズ」となっている。この違いだが、

・プラットフォームの名称 : Opteron 6000シリーズ

・CPUの名称 : Opteron 6100シリーズ

となっている。Fruehe氏によれば「Bulldozer世代のCPUはOpteron 6200シリーズになるだろうが、その場合でもプラットフォームはOpteron 6000シリーズのままとなる」という話だった。

ではなぜ上の文章でOpteron 6100シリーズと書いてないかというと、恐らくBulldozerの世代も、MCMを使った2ダイ構成になると予測されているためだ。Opteron 6000シリーズに含まれるCPUはいずれもMCM構成となることを前提としているため、敢えてOpteron 6100シリーズとは書かなかったので、その点に留意されたい。これについては、この後の文章も同じである。