|

|

|

説明を行った三洋半導体ハイパーデバイス事業部 スモールデバイス開発部の秋庭隆史部長 |

三洋半導体は4月2日、携帯電話などのパワースイッチ、D/DコンバータなどのMOSFETとして、アップドレイン構造を採用することで従来に比べて大幅な小型・薄型化と低オン抵抗化を可能にしたEFCPシリーズを発表、説明会を行った。

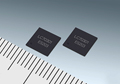

今回発表したのはPチャネル(Pch)品「EFC4301」「EFC4302」の2製品、Nch品「EFC4402」の1製品である。これらの製品はモールド樹脂やフレーム金属を使用しておらず、原材料の省資源化が可能であり、かつ完全鉛フリー・ハロゲンフリーという環境配慮型製品となっている。

|

|

|

同じく説明を行った三洋半導体ハイパーデバイス事業部 スモールデバイス開発部MOSデバイス課の吉村課長 |

従来の3端子MOSFETは、ソースがチップ表面に、ドレインは裏面に配置される縦型構造をとっている。このため、表面実装用パッケージとするためには、チップ裏側のドレイン電極から、パッケージへの実装時にソースと同面にある端子へと引き出す必要があった。このため、パッケージはプラスチックなどの樹脂モールド型となり、樹脂や基板などの厚さのために薄型化、小型化の面で制約があり、パッケージコストの引き下げという点でも限界があった。

これに対して、今回採用した「アップドレイン構造」は、ソース部の直下にゲート部を挟んでドレイン部を設け、チップ基板内部の経路を通ってチップ表面のドレイン電極に電流を引き出すことで、ドレイン、ソース、ゲートの3端子をすべて同一面に配置することを可能にしたもの。これにより、モールド樹脂や基板を必要としないチップ・スケール・パッケージが使用できるようになることから、今回発表した3機種は高さ0.37mm、面積1.0mm×1.4mm×0.37mmという小型・薄型化を実現した。

これは既存同等製品(MCH6305)比で高さでは56%減、面積は66%減となっている。また、重さも86%の削減に成功し、1mgを達成している。また、同社第4世代となる0.25μmトレンチプロセスによる微細化とチップ内部の経路からドレイン端子への引き上げのためにドレイン端子下に高ドーズ層(低抵抗層)を設ける新開発のHDDL(High Doped Difusion Layrer)構造により、Pch:50mΩ、Nch:27mΩ(いずれもVGS4.5V時のtyp.値)という最高水準の低オン抵抗化を実現している。

この小型・薄型化、低抵抗化により、携帯機器の極薄化、小型軽量化、駆動時間の長時間化に貢献することができるという。