CrayのX-MP/2と富士通のVP-200の基本演算性能を比較してみると、割り算以外の大部分の演算でVP-200の方が高い性能を持っていた。

VP-100/200がCray X-MPに比肩する性能を持つことが出できたのは、AmdahlのECLテクノロジを使って高速のCPU、高速のベクタユニットを作れるようになったからである。このECL LSIの製造を担当した富士通の半導体部門は、歩留まり低下要因を順次潰して安定供給ができるようになり、M-190、M-380、そしてVP-100/200が作れるようになった。

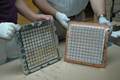

400gateのロジックLSIのゲート遅延は350psである。1300gateのチップはレジスタファイルを作るのに用いられた。そして、4Kbit SRAMのアクセスタイムは5.5nsであった。これらのチップは空冷であり、多重の仏塔のような放熱フィンがつけられていた。このフィンはパゴダフィンと呼ばれていた。

-

図2.10 VP-100/200に使用された400GateのECL LSI(右側)。左は1Kbitチップを4個搭載したSRAMモジュール (出典:情報処理学会Computer Museum)

これらのLSIは11×11=121個のLSIを搭載できるMCC(Multi Chip Carrier)と呼ぶ多層プリント基板に搭載され、次の図のように、13枚、あるいは15枚のMCCを積み上げる形で実装された。

MCCとサイドパネルの間は、Zero Insertion Force(ZIF)コネクタで接続されている。ZIFコネクタは前方からMCCを挿入するときはコネクタ接点は接触せず、通常のコネクタの場合と違ってMCCの挿入に必要な力はゼロである。そして、挿入を終わってからMCCの両脇に見えるネジを締めることによりコネクタを接触させる。

-

図2.11 最大121個のLSIを搭載するMCCを13枚、あるいは15枚スタックし、ZIFコネクタを備えた両側のサイドパネルでMCC間の接続を行う実装であった (出典:情報処理学会Computer Museum)

Amdahlの技術を学ぶことにより、富士通のLSIと実装技術は大きく進歩し、VP-100/200を作れるようになった。しかし、先進的なAmdahlの技術は製造性が悪く、本当に製造が出来るレベルの技術を完成したのは富士通であった。

つまり、富士通は本気でやればできる技術ポテンシャルを持っていたのであるがぎりぎりの挑戦はしておらず、Amdahlとの共同開発で尻を叩かれて、その技術ポテンシャルが開花したというところであろう。

(次回は5月24日の掲載予定です)