産業技術総合研究所(産総研)と東京電機大学(電大)の両者は12月8日、量子コンピュータの基礎となる量子ビットに存在していた、ある程度の時間で特性が変化しては元に戻ることを繰り返すという長周期の特性変化という課題について、半導体材料であるシリコンを用いて製造されるシリコン型量子ビット素子に関し、その原因を特定することに成功したと共同で発表した。

同成果は、産総研 先端半導体研究センター 新原理シリコンデバイス研究チームの岡博史主任研究員、同・浅井栄大主任研究員、同・加藤公彦主任研究員、同・森貴洋研究チーム長、電大の森山悟士教授らの共同研究チームによるもの。詳細は、12月7日~11日に米・サンフランシスコで開催のIEEE主催の半導体および電子デバイスに関する世界最大の国際会議「IEEE International Electron Devices Meeting(IEDM) 2024」にて発表の予定。

量子ビットに起こる長周期の特性変化が課題となるのは、状態が変化したままだと量子ビットが意図した状態にないため、計算結果にエラーが生じてしまうからだ。それを防ぐためには、特性変化の周期を考慮して定期的に状態診断を行い、その調整作業を行う必要がある。しかし、現在実用化されている量子コンピュータでは診断を高頻度に行う必要があり、なおかつ調整には数時間を要することもある。その結果、ユーザーの量子コンピュータの利用時間を制限してしまっている状況だ。

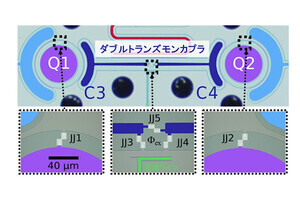

量子ビットを実現する方式は複数存在しており、そのうちの1つであるシリコン型においては、長周期で電流-電圧特性が変化する現象が観測されている。シリコン型の内、高集積化への期待が高いことから研究開発が進むのがFin型であるが、そのFin型でもこの長周期の特性変化の原因は未解明で、実験的な検証も十分に進んでおらず、高度で実用的な量子計算を可能にする高集積量子コンピュータの安定な動作を実現するため、その原因解明が望まれていた。そこで研究チームは今回、これまで産総研で取り組んできたシリコン型量子ビット素子の研究と、トランジスタの評価・解析手法を応用し、Fin型の長周期特性変化の原因を詳しく調べたという。

Fin型の周期的な特性変化は、数十秒程度の間隔で電流値が変化しては元に戻るというもの。Fin型は、量子情報を担う電子をシリコン中に閉じ込める必要があるため、電圧を印加することでシリコン中の電子や正孔の密度を制御する役割を持つ「ゲート電極」を多数利用する。ゲート電極ごとに異なる電圧を設定する必要があることから、周期的な特性変化をもたらす要因がどのような電圧条件で生じるのかを特定するには、量子ビットの動作原理上、非常に困難だったという。そこで今回の研究では、Fin型と同じ材料・構造で、ゲート電極が上部に1つしかないシンプルな素子によるトランジスタの利用が考案されたとのこと。この構造であれば、ゲート電圧条件を変えながら、電流値の時間変化の追跡が可能になるとする。

ゲート電圧を大きくすると、電流値が増大し、オフ領域からオン領域に移る。各領域において一定の電圧下で、電流値の時間変化を追跡した結果、オフ領域とオン領域では電流値が安定しているが、両領域の間の「サブスレッショルド領域」の電圧条件においてのみ電流値が数十秒間隔で増大と減少を繰り返す、周期的な変化が確認された。これは、Fin型における周期的な特性変化が、サブスレッショルド領域の特定の電圧条件において生じていることを示唆しているという。

サブスレッショルド領域の電圧条件では、トランジスタの特性はバンドギャップの端(バンド端)に近い部分の影響を強く受けるため、研究チームはこれらの結果について、バンド端に電流値の変化を引き起こす要因として、電子をトラップする準位が存在することを意味しているとする。実際に、周期的振幅を従来のモデルに基づいて計算すると実験値を再現できないが、バンド端に、電子や正孔の捕獲・放出の原因となる「トラップ準位」が存在すると仮定すると、実験データとの一致が確認できたとしている。

研究チームの先行研究から、典型的なトランジスタの場合、バンド端のトラップ準位は絶縁膜と半導体の界面の欠陥に由来することが判明している。トランジスタにおけるスイッチング特性の劣化原因について解明したこの時の知見に基づくと、観測された長い周期での特性変化は、絶縁膜と半導体の界面で生じる電子のトラップ現象が原因であることがわかったとのこと。つまり、周期的な特性変化の抑制には界面の品質が鍵であることが突き止められたのである。

今回の研究成果により、シリコン量子ビット素子の安定動作につながる製造技術に関する指針が得られたとする研究チームは、今後も得られた知見に基づき、Fin型の試作と動作検証、および界面の高品質化を含めたプロセス技術の開発を進めていくとしている。