米Intelが10月9日、高性能モバイルノートPC向けの次期主力プロセッサ「Panther Lake」(パンサーレイク、開発コード名)の技術詳細を発表した。同社が米アリゾナ州に新設した半導体製造工場「Fab 52」で導入した新たな半導体製造プロセス、「Intel 18A」によって生産する最初の製品となる。従来プロセッサ比で省電力性と処理速度を高め、AI性能も大きく強化した。今年後半にかけて量産化を進め、2026年初頭からPC市場での本格普及を見込む。

-

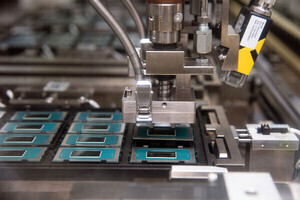

米Intelが今月、報道関係者向けに公開したPanther Lakeプロセッサ。写真に2種類の製品が写っているが、どちらもPanther Lakeだ。複数のチップを組み合わせて製品バリエーションに柔軟性をもたせた製品であるため、基板上のチップの規模が異なる

Panther LakeのCPUチップを切り分ける前の300mmサイズの半導体ウェハ。目下、Intelがアリゾナに新設したFab 52で量産化が進められている。Panther LakeならびにIntel 18Aの成功に、まさに同社は社運を賭けている状況だ

Panther Lakeでは、処理性能が現行製品との比較で最大50%以上向上することをうたう。CPUは利用場面に応じて高性能チップと省電力チップを切り替えるハイブリッドコア構成とすることで、現行製品比で同等の性能を50%以上低い電力で引き出し、同等の電力であれば30%以上高い性能で実行できるという。内蔵する統合型GPUは「Xe3」と命名された新設計のものへ改良し、現行製品比で50%以上高い性能、かつ競合他社に対しても性能優位であることをアピールしている。

-

Panther Lakeと現行製品(Lunar LakeおよびArrow Lake世代のIntel Core Ultra)との性能比較を並べた資料。ピーク性能だけでなく、電力当たり性能の大幅改善も強調している

-

Panther Lakeのハイブリッドコア構成。ハイブリッドな点では従来を引き継ぐが、高性能チップ(P-Core)と省電力チップ(E-CoreならびにLP E-Core)の設計はそれぞれ刷新。P-CoreとE-Core/LP E-Coreへのタスク割り当てを効率化し処理効率を上げる仕組みも改良されている

Panther Lakeのシングルスレッド性能をLunar Lake/Arrow Lakeと比較した資料。縦軸が性能で横軸が消費電力。より低い消費電力で同等の性能を出せ、同等の電力でより高い性能を出せる

Panther Lake搭載の試作機も含め、ノートPCの実機を動作させて、実際に同じ処理を実行した際の消費電力を比較している様子も披露した。オンラインとオフラインの処理を組み合わせプロセッサへ満遍なく負荷をかけている環境で、リアルタイムでモニタしていてもPanther Lake機の消費電力が常に最も低い状態だった

-

Panther Lakeにおける、AI性能の指標であるTOPS(Tera Operations Per Second、1秒あたりの演算回数)の数値はチップ全体で計180TOPS。Microsoftらが定める「Copilot+ PC (AI PC)」の要件である40TOPSはもちろんクリアしている

またPanther Lakeは、CPU、GPU、I/Oといった役割別の半導体チップ(半導体ダイ)を個別に製造し、これら複数のチップを基板上で統合する手法を採ることで、用途にあわせた柔軟な製品バリエーションが可能な製品であることも特徴としている。これにより、同じPanther Lakeで高性能な大型ゲーミングノートPCから、バランスのとれたオフィス向けモバイルPC、省電力な携帯ゲーミングPCまでカバーできるスケーラブルな設計とした。

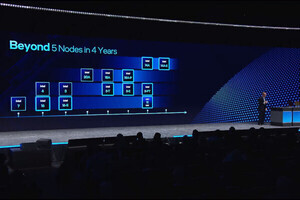

Intelの半導体製造プロセスは現在までに、2nmプロセス相当の「Intel 20A」が開発されていたが、一転して主力プロセッサでの採用を見送り、一歩進んだIntel 18Aの開発に注力していた。Intel 18Aの半導体プロセスノード(半導体トランジスタ回路の最小線幅などで表す製造技術の世代、小さいほど微細化しており回路集積度が増す)をIntelは「2nm以下」としており、1.8nmノード相当とも言われる同プロセスでの生産が成功すれば、TSMCやSamsungが今年後半に量産を予定し、ラピダスが今年夏に試作に成功(量産は2027年目標)した2nmプロセスに対しても世界最先端の半導体製造技術が実現したことになる。

Intel 18Aでは、重要なブレークポイントとして「RibbonFET」と「PowerVIA」という2つの技術が盛り込まれている。RibbonFETとPowerVIAの技術確立は、今後の半導体微細化の進展にも明るい材料となる。

RibbonFETはIntelの用語で、他社は主にGAA FET(Gate All Around FET)などと呼んでいるもの。半導体のトランジスタの仕組みの一種で、従来Intelが使用してきたFinFETが平面構造のトランジスタを立体構造へと進化させることで半導体の回路集積度を上げていたところ、さらに立体構造を進めて垂直方向に回路を構成できるようにした。回路集積度や省電力性がFinFETよりも向上するが、GAAは技術難易度が高く、量産ではこれまではSamsungが3nm世代で導入したのみ、TSMCは2nm世代で採用する計画、ラピダスは今年夏に試作品の製造が成功したという段階だ。

-

こちらがFinFETのイメージ。電極は上下左右3方が囲まれ、まさにフィンのよう水平に並べられている。一方の先のRibbonFETでは、電極の4方(つまりAll Around)が囲まれ垂直方向に積まれている

PowerVIAはIntel独自の技術で、従来は半導体トランジスタの表面(上側)に混載していた信号配線と電源配線のうち、電源配線をトランジスタの裏面に移設したもの。半導体プロセスノードの微細化の進展にともなって信号配線と電源配線の配置のやりくりが困難になり、電圧や信号が不安定になりやすいなどの問題が出てきていたものが、これで解決すると期待されている。

ほかPanther LakeとあわせてIntelは同日、データセンター向けプロセッサ「Clearwater Forest」(クリアウォーターフォレスト、開発コード名)も発表した。従来製品比で倍増となる1ソケットあたり最大288基もの省電力コアを搭載するXeonプラットフォームのプロセッサで、Panther Lakeと同様にIntel 18Aで生産する。他社競合製品と対抗する切り札として重要なプロセッサ製品であり、「Intel Xeon 6+」のブランド名で2026年の市場投入を予定している。