英ARMはCOMPUTEX TAIPEI 2015開催前日の6月1日に台北にて記者説明会を行い、Cordio IPとCortex-Mに関する新IPを発表した(Photo01)。

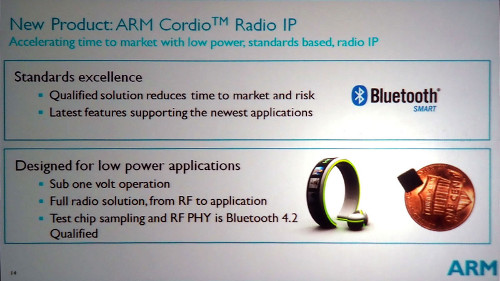

さて、発表の一つ目はCordio IPに関するものだ。CordioはARMが提供するRF関連のIPである。

中核になるのは米Sunrise Micro Devicesが提供していた、Sub 1Vで動作するBluetooth IPである。Sunrise Micro Deviceはフロリダをベースとしていた会社で、ARMから出資を受けて作られた会社である。2014年3月まではStealth Modeで動いており、その後製品発表に合わせてStealth Modeから脱している。

同社はBluetooth 4対応のRADIO IPをTSMCの55nm LPプロセスで開発しており、動作電圧は0.95Vと低いことが特徴であった。その後同社はARMに買収され、Cordio 4という製品がCordio IPとしてARMから発売されるようになった。今回の発表はこのCordio IPがBT 4.2に対応したといものだ(Photo02)。

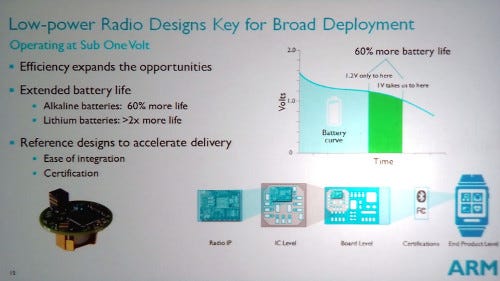

Cordioの最大の特徴は動作電圧が低いことで、この結果としてバッテリー電圧が定格ではもちろん、落ちてきた状況でも問題なく通信ができることである(Photo03)。

アルカリバッテリーで最大60%、リチウムイオンでは最大2倍にバッテリー寿命を延ばせるというのは、そこまで電圧が降下する状況まで使い続けられる、という意味である。

発表を行ったDipesh Patel氏(EVP of Technical Operations)は、実際に動作するCordioベースの評価チップ(Photo04)を示しながら、Wearable機器とか、あるいはBeaconなどにも最適だと説明する。

ちなみにこのチップそのものはCortex-M0+コアにCordioを組み合わせ、実際に動作するものだそうだが、あくまで評価用ということでSRAM/Flash容量はそれほど大きくない。そのため、mbed OSは載らないとのことだ。もっともARMがチップ自身を製造するわけではないので、パートナーがmbed OSの動くCordioベースのチップを作ることは十分可能という話であった。

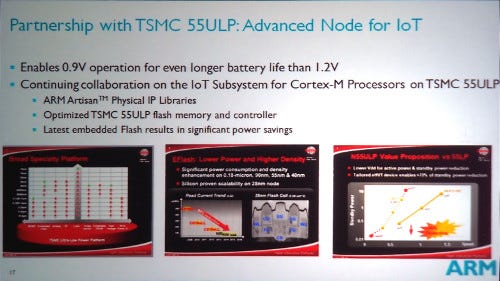

2つ目の発表は、その55nmに関する話だ。ARMはIoT Subsystem for Cortex-M ProcessorというIPを発表した(Photo05)。これは何か?というと、TSMCの55nm ULPプロセスに最適化された、Memory ControllerとCache、Power Management、Interconnetなどをひとまとめにしたものだ。

ターゲットとなるのはTSMCの55nmのEmbedded Flashで、これを使ってMCUを作る際に必要な機能をまとめた形になる。従来ARMはCPUコアのみを提供していた。そのため、SRAMの容量や構成、Flash Memory周りなどはライセンスを受けた各社がそれぞれ実装し、差別化を行ってきた。そこにARMがどうこうという話はあまりなかったのだが、今回はそこから一歩踏み込んだ形になる。

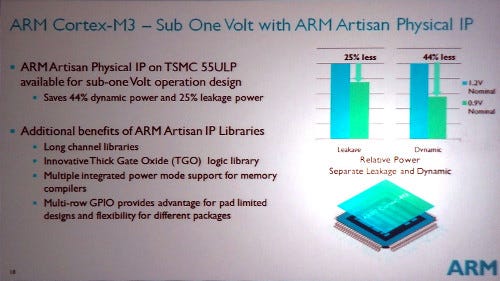

これと組み合わされるTSMCの55nm ULPは0.9V動作が可能になるプロセスである(Photo06)。まだTSMCのWebサイトには55nm ULPの詳細が記載されていないが、基本は55nm LPプロセスの特徴を生かしつつ、Vddを0.9Vまで下げることで大幅な消費電力削減を可能にしているとする。

|

Photo06:55nm ULPの存在そのものは、ARM Techcon 2014で明らかにされていた。ただ提供時期は2015年中にRisk Production開始という話だったのだが、これがProduction Readyになったということか |

実のところ55nmプロセスはすでに自動車向けのFlash MCUでは広く使われていた。理由は大容量のFlashである。特にECUに求められる機能が増えた上、機能安全を盛り込むという場合、大容量のFlash Memoryが必要になる。

ただ、外付けで大容量Flashを接続するのは部品原価と実装面積の点で不利だし、外付けにする時点で故障確率が上がるからできれば避けたい。一方で、180nm~90nmプロセスのまま大容量Flashを搭載したら、ダイサイズが極端に肥大化する。55nmへの移行はこうしたジレンマを解決するための方法である。

では汎用MCUではどうか? というと、ひとつは微細化による動作電圧低減で消費電力を増やそうという目的があるが、もうひとつはやはり大容量化が必須になりつつあることだ。

例えばmbed OSはまだ正式にはMinimum Requirementが発表されていない。ただ、一通りのNetwork StackやSecurity Featureを載せて使おうとすると、SRAMが64KB程度は欲しいとされるし、プログラムの方もそれなりに肥大化するからFlashの容量は大きく取りたい。SRAM容量を増やすには微細化するのが一番で、例えば90nmで20KBの容量を確保するのと同程度のエリアサイズで、55nmならば64KBが確保できる。

MCUに要求されるニーズが増えつつある現状では、微細化はまだ効果的である。Flashの方も同じで、複数のNetwork StackとかProtocol Stackを載せるためには、やはりそれなりのFlash Memoryが合ったほうが良い。

また、最近On-the-Air機能、つまり複数バンクを用意し、片方のバンクからシステムを動かしつつ、もう片方のバンクをアップデート用に確保することで、稼動状態でのファームウェアアップデートを可能にしたいというニーズも増えているが、これを行うためには必要となるFlashの容量がきっちり倍になる。こうしたことへの対応にも、55nmへの以降は良い解になる。

これに対して、ARMはCortex-M3をターゲットとしたTSMC 55ULP用のArtisan Physical IPを提供するとしており(Photo07)、これを使った製品は早ければ年末頃には登場するかもしれないとしている。

うがった見方をすれば、これもmbed OS普及に向けた手のひとつなのかもしれない。55nmで製造されたCortex-Mは性能/消費電力比が現在のものよりずっと優れたものになりそうだが、それに向けたソフトウェアとしてmbed OSがすでに準備されているというのであれば、mbed OSを使わない理由はあまりない。

本来なら明らかに逆な気がするのだが、単にWearable向けに最適なソリューションを提供、という以上の何かを感じさせるものであった。