米Intelは9日(現地時間)、"Haswell-EP"の開発コード名で知られていたIntel Xeon E5-2600 v3シリーズおよび、Intel Xeon E5-1600 v3シリーズ製品を発表した。これに先駆けて日本国内で製品の詳細が説明されたので、その内容を簡単に紹介したい。

Haswell-EPは3種類シリーズ32製品

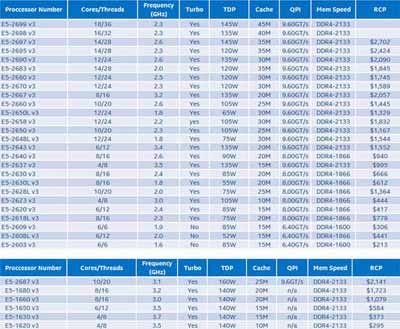

今回発表された製品は2P構成のXeon E5-2600 v3シリーズが27製品、Xeon E5-1600 v3シリーズが5製品となっている(Photo01,02)。またダイは後述するが3種類のバリエーションがある。

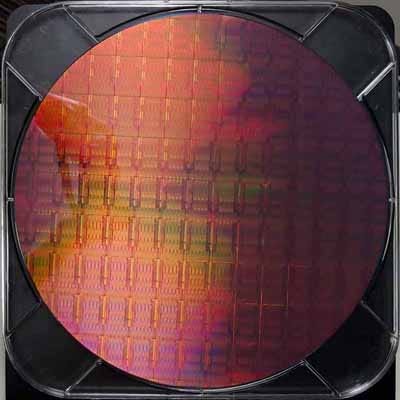

現時点でダイサイズなどは公表されていないが、最大18コアを搭載するだけにかなり大きい。Photo03は14~18コアのものと思われるウェハの写真だが、300mmウェハから85チップしか取れないことからもダイサイズの大きさがうかがえる。

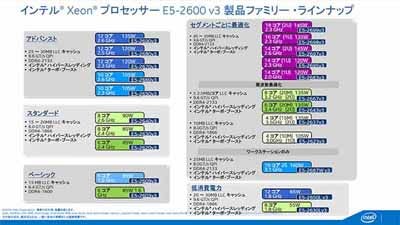

製品一覧はPhoto04の通り。同社はこれを5つにカテゴライズしている。

Haswellコアの周囲に多くの拡張機能を搭載

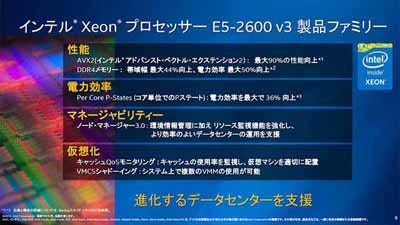

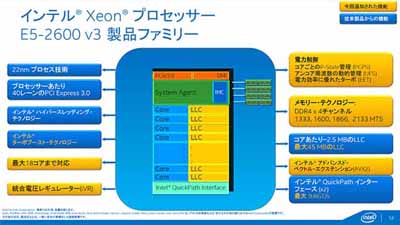

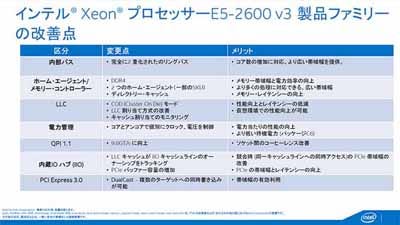

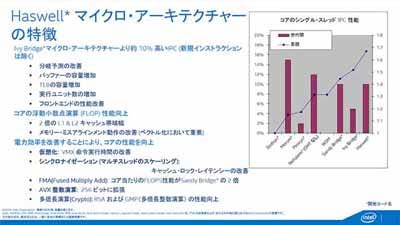

Photo05が主要な特徴である。従来(IvyBridge-EP)製品との大きな違いは、アーキテクチャがHaswllベースとなり、またDDR4メモリーをサポートしたことだが、ほかにも細かな機能追加がなされている(Photo06)。

コアそのものは従来のHaswellと同じであり、コア数のほかにIVRやこれに基づく電力管理などはHaswellベースのCore iプロセッサを基にしたものだ(Photo07)。

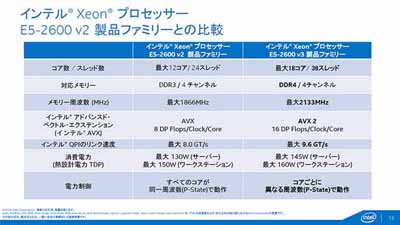

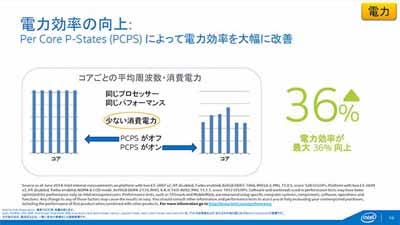

Photo08が従来製品との差をまとめたものである。TDPはやや増えているが、全体としては性能を大きく引き上げる方向になっている。その一方で、DDR4の採用により性能を引き上げながら消費電力を下げたり(Photo09)、コアごとに異なるP-State、動作周波数、動作電圧を供給することで、平均36%の効率改善が図られているとする。

|

Photo10:IVRは先にも書いたとおり、まだオンパッケージであってオンダイでは無いと思われる。これはPhoto02で信号ピンの無い空白部に、明らかにインダクタンス(コイル)と思しき部分が見られることから明らかである |

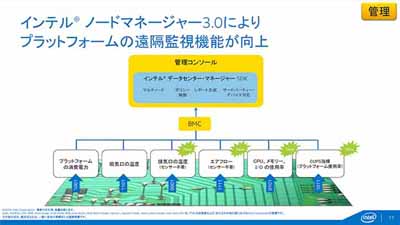

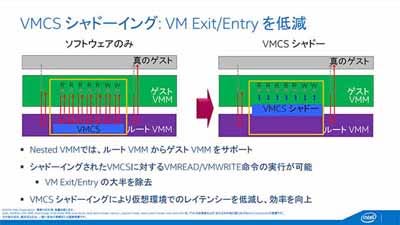

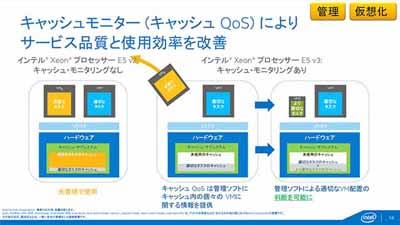

Core iプロセッサとは異なるのは管理機能(Photo11,12)や仮想化機能(Photo13)である。CPUとは別にIntel Node Managerを使って動作状態を常時監視したり、(これは後で出てくるが)キャッシュの利用状態をタスク単位で監視して、キャッシュの割り当て方を調節するといった事が可能となっている。またHaswell-EPでは、仮想環境を2段にネストすることが可能であり、運用の柔軟性が図れるとしている。

|

Photo12:ここではVM単位での説明となっているが、実際にはTask単位でLLCの利用率を監視できる。ただそのTaskを最終的にVMに紐付けることで、VM単位でのチューニングが出来るという話である |

|

Photo13:レガシーVMM/ゲストVMMがこれまで利用してきたVM Managerであり、この下に新たにルートVMMと呼ばれるものを置くことができるという話。ただこれは新しいNested VMMに対応する必要があるので、既存のレガシーVMM/ゲストVMMがそのままルートVMMになれるわけではない |

内部構造

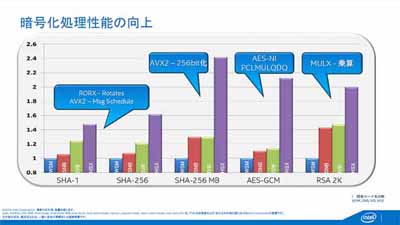

ではもう少し内部の詳細を。まずCPUコアそのものはHaswellそのもので、ここでは特に違いは無い(Photo14)。暗号化処理もAVXやAES-NIなどにより大幅に改善されている(Photo15)が、これもHaswellの特徴そのままである。

|

Photo14:ちなみにTransaction Memory(TSX)に関しては問題が見つかったことで、このHaswell-EPでは「実装はしているが無効化している」との事で、これが修正されるのは続く"Haswwll-EX"になる予定 |

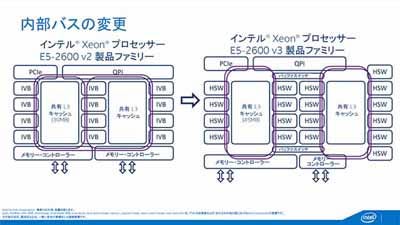

ではその外側は? というと、いろいろと細かな違いがある(Photo16)。まずRing Busであるが、IvyBridge-EPでは3つのリングバスが多重構造になってプロセッサあたり2つずつのRingにアクセスできる構成になっていた。これに対し、Haswell-EPでは完全にRing Busが2つに分離され、間にBuffer Switchが入る構造になっている(Photo17)。

|

Photo17:普通に考えるとBuffer SwitchはLatencyが増える形になるが、後で出てくるCODモードではこれがSnoop Filterとして動くことで効率を改善する仕組みになっており、案外悪くない選択なのかもしれない |

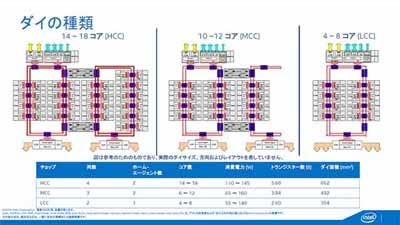

一方のダイであるが、8コア/10コア/18コアの3種類のダイが用意される。このうちローエンドにあたる8コアのみRing Busが一組で、あとはRing Busが2組となる構成だ(Photo18)。

IVRに関してはこれはほぼHaswellと同じ仕組みで、コアやSystem Agent、I/Oなどにそれぞれ個別にIVRが搭載されている。そのため、外部からはメモリ用と統合入力の2種類の電源を供給すれば良い仕組みとなっている(Photo19)。

システムとしてみた場合、煩雑に動作周波数やP-Stateを変更しても、CPUの外部に電圧レギュレータが搭載されていると、これが追従するまで時間が掛かる。なので、省電力モードに入るまでに時間が掛かり(=余分に消費電力が増える)、さらにそこから抜けるにも時間が掛かる(レスポンスタイムが増える)ことになる。

IVRの場合、反応時間を1桁以上削減できるとしており、これはよりすばやく省電力モードに入ったり、そこから迅速に復帰できるわけで、性能改善と省電力性の両方に貢献することになる。

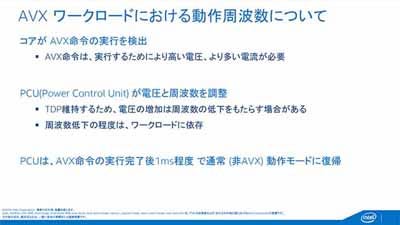

また電源周りでは新たにAVXモードが実装された(Photo20)。これはAVX命令を実施する場合の電圧を引き上げる仕組みである。ちなみに動作の詳細は不明だが、恐らくある程度ヒステリシス(連続してAVX命令が実行される、など)を見てこのモードに入るといった仕組みを用意していると思われるとのことだった。

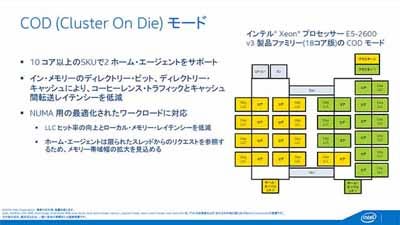

次がLLCに絡む話である。従来のXeonの場合、10コアなら10コアがまとめて一つのメモリアドレスを共有するUMA(Unified Memory Address)方式で実装されている。ところがHaswell-EPからは新たにCOD(Cluster On Die)モードが搭載された(Photo21)。

これを利用した場合、システム内部に2つのProcessor Clusterが生成され、それぞれが別々のメモリコントローラを占有する形になる。従って、この場合Cluster 0とCluster 1はNUMA(Non-Unified Memory Address)アーキテクチャとして動作することになる。

この方式のメリットは、LLCのヒット率の改善である。特に2つのVMが動いており、それぞれが全く異なる作業を行っているようなケースでは、UMA方式はむしろSnoopingのトラフィックが無駄に増える事になるので、むしろ細かくClusterに分け、もう片方のClusterにSnoopingが行かないようにする方が性能が改善する。この際に、先ほどPhoto17で出てきたBuffer Switchが、Snoop Filterとして働くことになる訳だ。

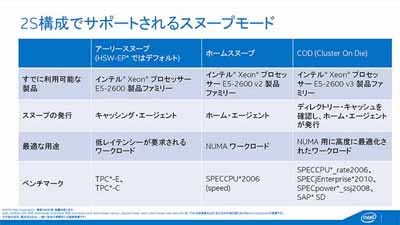

別にHaswell-EPでは無条件でCODが使われるわけではなく、Early Snoop/Home Snoop/CODの3種類が利用できるので、利用する用途に合わせて構成を変更できるとしている(Photo22)。

|

Photo22:低コストのサーバをスケールアウト的に並べる、いわゆるクラウド的な構成は基本的にNUMAであり、そうなると例えば18コアのCPU×1よりも9コアのCPU×2の方が使いやすい、ということは十分考えられる |

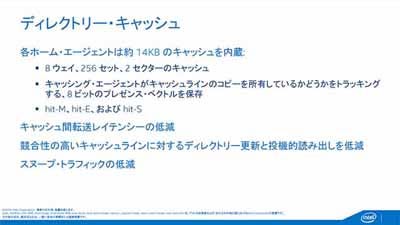

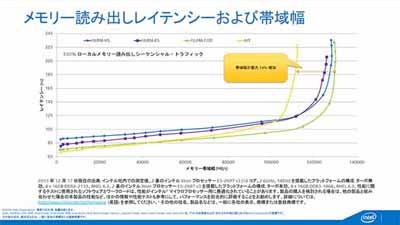

またメモリコントローラがぶら下がるHome AgentはHome Snoopの場合、Snoopの発行元となるが、この場合に備えて内部にDirectory Cacheを搭載することも明らかにされている(Photo23)。これによる性能改善の度合いを示したのがこちら(Photo24)である。

|

Photo24:Latencyの絶対値で言えばコア数が少なく、Bufferも入っていないIvyBridge-EPの方がオンキャッシュの領域ではレイテンシが低いが、DDR3の帯域がネックとなることが判る |

グラフでは9コア×2構成の分、Snoopingの頻度が減ることで、CODが一番低レイテンシとなっているが、Buffer Switchをはさんでいるにも関わらずEarly Snoop/Home Snoopの場合でも驚くほどHaswell-EPのLatencyが低いことが分かる。またDDR4の効用で最大帯域が14%ほど向上している。

次が仮想化である。今回新たに搭載されたのがVMCSとEPTであり、これによりさらに仮想化環境の高速化が可能になったとしている(Photo25)。

まず大きいのがVMCS Shadowingである。これはゲストVMMが煩雑にVM Exit/VM Entryを行うようなケースで、実際のVMCSにアクセスするのではなく、ルートVMMの上に構築されたVMCS Shadowをアクセスするようにすることでアクセスの効率化を図るものである(Photo26)。

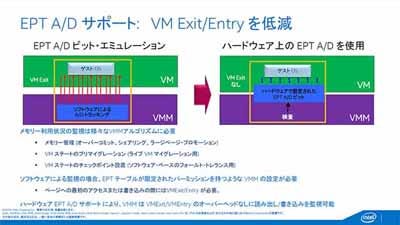

もう一つがEPT(Extended Page Table)のA/D bitへのサクセスの高速化である(Photo27)。どちらも要するにVM Exit/VM Entryを実行する頻度を減らすことで高速化しよう、というものだ。

|

Photo27:A/Dというのは"Accessed/Dirty"の意味で、そのページの状態を示すもの。従来はこれにアクセスするためにはいちいちVMを抜ける必要があったが、Haswell-EPではこのA/D bitの状態をVMMで保持するように出来る |

最後が先ほども出たキャッシュモニタリングである(Photo28)。これはそれぞれのTaskがLLCをどう利用しているか、というデータをモニタリングする機能で、これを利用して性能を改善できるという話である。

なお、このHaswell-EPことXeon E5-2600 v3シリーズ/E5-1600 v3シリーズの正式発表は、間もなくサンフランシスコで開催されるIDFとなると思われる。