エクサスパコンに必要なメモリ量とメモリ性能は

アプリケーション作業部会は40種のアプリケーションについて調査を行ったが、性格の似ているアプリケーションは重複を排除して、28種のアプリケーションの要求メモリ量とメモリバンド幅をプロットしたのが次の図である。

この図のように要求メモリ容量は1TBから1EBまでの広がりがあり、要求メモリ帯域は0.0001Byte/Flopsから4Byte/Flopsという広がりがあることが判明した。これを1つのシステムでカバーしようとすると、メモリバンド幅、メモリ量、演算能力の1つ以上が余ってしまいムダが多いので、要求メモリ量は少ないが高いメモリ帯域を要求する「メモリ削減」型、要求メモリ容量は中くらいで、要求メモリ帯域も少なく、演算能力だけが重要という「演算重視」型、大きなメモリ容量とメモリ帯域を要求する「容量・帯域」型、中くらいのメモリ容量とそこそこのメモリ帯域の「汎用」型という4種類のアーキテクチャのスパコンでカバーするという考え方を打ち出した。

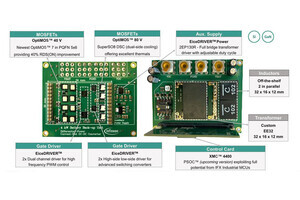

次の表は、現在の技術トレンドをベースにこれらの型のアーキテクチャのスパコンの諸元を予想したものである。なお、この表にある型は当初の検討のもので、ベースラインは汎用、SoCはメモリ削減、アクセラレータは演算重視、バンド幅は容量・帯域に対応している。

|

|

現在の技術トレンドで予測した各アーキテクチャ型のマシンの諸元。メモリ容量は演算性能1TFlopsあたりの値、消費電力は1EFlopsの構成の場合の値で、演算性能とメモリバンド幅は20MWの消費電力のシステムとした場合の値である。(出典:SS研での牧野教授の講演資料) |

ベースラインは20MWの消費電力で1ExaFlopsを実現できるという見込みであり、SoCは2-5MW、アクセラレータは4-10MWで1ExaFlopsという見込みである。また、バンド幅重視型はB/Fを1、メモリ容量を1EBとすると消費電力は120MWの見込みで、電力を20MWにすると0.15EB/sのメモリ帯域、0.15EFの演算性能に制限されてしまうという予想である。

なお、この性能トレンドの見込みは楽観的であり、2018年にこの数字の達成は難しいという声もあり、これらの諸元も容易に達成できるというものではない。

牧野教授は「アプリケーションから-「欲しかったのはこれじゃなーい!!」と叫ばないために」と題した講演で、「京」の目標設定と開発を振り返り、目標設定をきちんと行わないと、出来上がったときに、「欲しかったのはこれじゃなーい!!」と叫ぶことになってしまうと述べた。

実は、このタイトルには下敷きがあり、ザリガニワークスという会社がコレジャナイロボという製品を出している。ガンダムが欲しかったのに、詳細をはっきりさせなかったためにプレゼントがこのロボになってしまい、「欲しかったのはこれじゃなーい!!」と叫ぶというわけである。

「京」の場合は、そのスタート時点で各分野から21種のアプリケーションを集めたが、最終的には、その中の7種のアプリと、Top500のHPL(高性能LINPACK)とHPC Challengeの表彰対象になるFFTの合計9種の性能だけが指標となった。そして、HPLで10PFlopsを達成し、消費電力は20MW以下であることが必須の条件で、その範囲の中で、その他のアプリケーションの性能をできるだけ高めるということで、富士通のスカラとNECのベクトルの設計コンペティションが行われた。

その結果、両者の設計は、基本方式はスカラとベクトルという違いはあるが、プロセサチップのFlops、メモリバンド幅などの重要なパラメタは似たような値になり、次に示す性能比較でも両者の性能はほぼ同じになってしまい、スカラとベクトルの特徴が出ない設計になってしまった。

古典MDや量子化学はメモリバンド幅もネットワークバンド幅もあまり要らない。流体はメモリバンド幅が欲しい。QCDはメモリ量はいらないが、メモリバンド幅もネットワークバンド幅も欲しいというようにアプリケーションによって要求に大きな違いがあり、1台のマシンですべての要求を満たそうとすると帯に短し襷に長しということになってしまうという。

結果として、京のSPARC64 VIIIfxとSequoiaに使われているBG/Qの計算ノードを比べると、京はメモリB/Fでは2.4倍、インタコネクトB/Fでは4倍のバンド幅を持っているが、Flopsあたり2.5倍電力を喰うという設計になってしまったと指摘した。