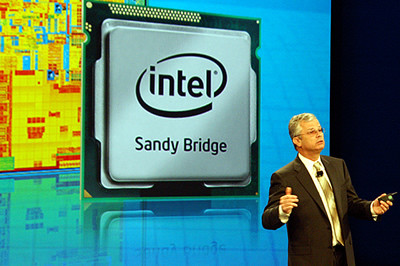

Intelの社長兼CEOのPaul Otellini氏による基調講演でIDF 2010が開幕した。続いて、同社のExecutive Vice Presidentで、Intel Architecture GroupのGeneral Manager、David Perlmutter氏が講演し、次世代CPUアーキテクチャ「Sandy Bridge」(開発コードネーム)の詳細を発表した。Perlmutter氏の講演を皮切りに、初日は各技術セッションでもSandy Bridgeの情報公開が相次いでいたので、ある程度まとめてレポートする。

Perlmutter氏はまず、「コンピュータはもっと直感的に使われるようになって行く」と話し、過去から現在に至るコンピュータの使われ方の歴史を振り返った。初期のコンピュータは貧弱なUIが使われ、テキスト程度を扱っていたものが、現在ではオーディオやビデオ、写真などの様々な体験ができるものになり、近い将来にはリアルタイム処理のモーションUIなども当たり前になって行くと、コンピュータがその使われ方さえも変わるほど更なる進化を遂げて行く未来を語る。その実現のためには更なるプロセッサパワーが不可欠とし、同社の新世代プロセッサの必要性を訴えた。

|

|

|

GestureTekが開発したm3Dカメラで撮影した映像を解析し、人間のジェスチャーを認識するモーションUIのデモ。リアルタイムでモーションキャプチャ解析をするには、高いプロセッサパワーが不可欠となる |

|

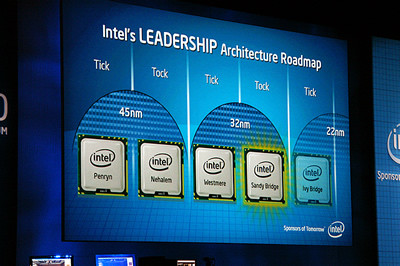

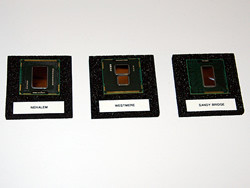

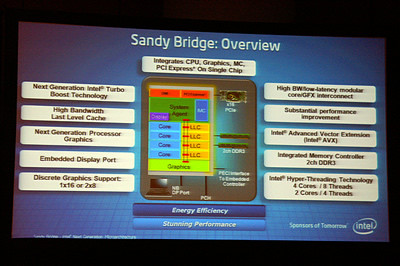

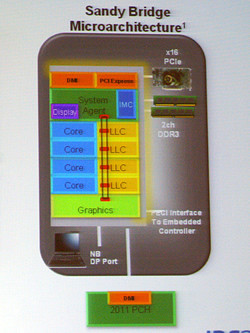

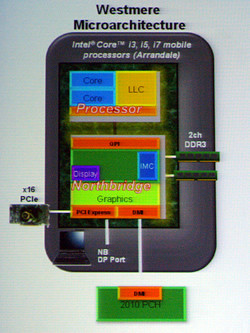

Sandy bridgeは、2年ごと交互にプロセス微細化とアーキテクチャ刷新を繰り返すIntelの「Tick-Tock」戦略で、「Westmere」の次世代のマイクロアーキテクチャだ。そしてSandy bridgeはアーキテクチャ刷新の"Tock"にあたり、これまで、WestmereでQPI接続のマルチダイ構成に留まっていたグラフィックスコアとの統合を完全な統合へと進めることや、浮動小数点演算性能の向上を狙ったベクトル命令セット「Intel AVX」の搭載などが大きなトピックとして伝えられていた。

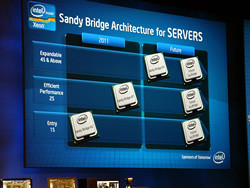

Perlmutter氏によれば、Sandy bridgeは、第2世代となるHigh-k/メタルゲートを採用した32nmプロセスで製造され、トランジスタ数は10億個に達するという。同氏は、「エンパイアステートビルは10億個のレンガで造られており、人間の脳には10億個のニューロンが存在する。これと同じ数のトランジスタを搭載するプロセッサが来年登場する」と、その集積規模の途方の無さをアピール。Sandy bridgeベースのプロセッサを搭載したPCは、来年早々に発売が始まる見込みとなっている。また、デスクトップやモバイルなどのクライアント向けだけでなく、Xeonなどのサーバ向けにも、来年前半にSandy bridgeが浸透する計画も語られた。

Perlmutter氏の基調講演では、Sandy bridgeにおける進化の概要として主に、データ幅を256bitへと倍増させたSIMD型ベクトル命令セット「Intel AVX」(AVX: Advanced Vector Extentions)による浮動小数点演算の高速化、より高いクロックアップが可能となった強化版Turbo Boost機能、CPUコアに完全統合されたグラフィックスコアのメリットなどについての説明がされた。

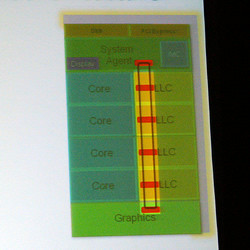

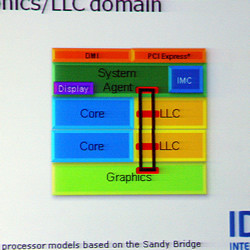

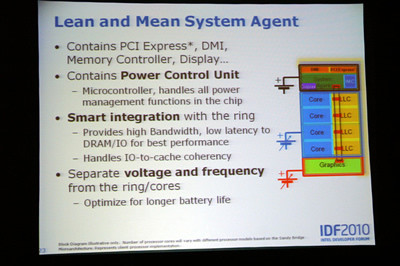

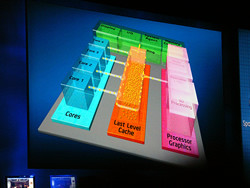

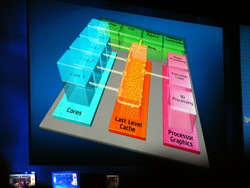

グラフィックスコアは、CPUコアと同一のダイの中に納まっており、さらに、CPUコアとグラフィックスコアで共有のLast Level Cache(LLC)を備えている。このLLCはCPUコアごとに対になるように(4コアなら4つ)設けられており、それらLLC部分を横断するように"リング"状になったインターコネクトでグラフィックスコア、おそびメモリコントローラ/PCI Expressなどを内蔵したSystem Agentと接続されている。この"リング"はLLCとの1接続あたり96GB/秒の帯域があり、CPUコア数=LLC数が4つのクアッドコアCPUであれば、帯域は384GB/秒となる。ほか、"リング"は、CPUコア数の増減に柔軟に対応できるスケーラブルな設計となっている点も特徴とされていた。

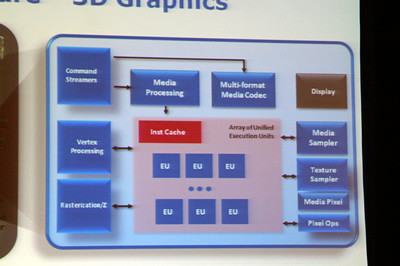

メモリコントローラ/PCI ExpressのSystem Agent部分とも直結のため、グラフィックスコアはそれらを低レイテンシかつ低消費電力で効率的に利用することができる。グラフィックスコアには、いわゆるプログラマブル・シェーダと考えられるUnfied Execution Unit(EU)を備え、ほか実装されたMedia Processing Unitを使って、このEUを動画エンコード処理などGPGPUに利用することもでき、また、主要動画フォーマットをサポートするコーデックのハードウェアエンジンなども内蔵されている。また、CPUコア、グラフィックスコア、System Agentはそれぞれ電圧や周波数が独立しており、モバイルPCのバッテリライフを伸ばせるような高効率な制御も可能となっている。ちなみに3Dゲーム動作の性能については、メインストリームゲームが快適に動作する程度とされた。

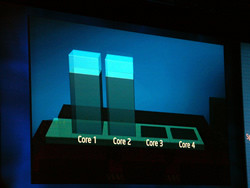

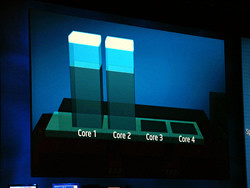

強化版Turbo Boostでは、NehalemやWestmereのTurbo Boostが動作中のコア数ごとに、それぞれ定められたbin数分のクロックアップをTDP枠内の範囲で行なうに留まっていたのに対し、ヘッドルームさえあれば、瞬間的なものになるが決められたTDP枠を超えるTurbo動作が可能となった。これは、負荷に応じてTurboがより機敏に反応動作できるようになったのと、あわせて新たに、CPUコアとGPUコアを含むプロセッサ全体をまとめて管理でき、よってサーマルなどのモニタリングがきめ細かくできるので、Extra Rangeを瞬間的に上乗せするような今回の強化版Turbo Boostが実現しているのだ。例えば、短時間に負荷が集中する、アプリ起動時といったような場面で、大きな効果があるものと考えられる。

このSandy Bridgeについては、IDFの会期中にわたって情報公開が行なわれているので、随時別稿にて詳細レポートをお届けする予定だ。引き続き注目いただきたい。

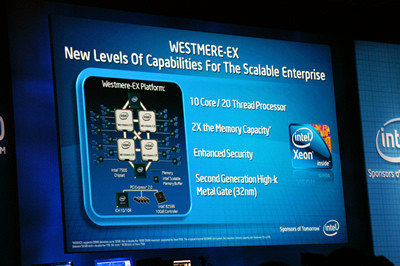

なお、当日のPerlmutter氏の講演では、Sandy bridge以外にも、現行のXeon 7500シリーズ(Nehalem-EX)の次世代製品となるMPサーバ向けプロセッサ「Westmere-EX」(開発コードネーム)も発表された。32nmのWestmereベースの10コアプロセッサとなっており、Hyper-Threadingでプロセッサあたり20スレッドを同時実行でき、さらに接続可能なメモリ容量は前世代の2倍に増えている。4ソケットのシステムであれば、40コア80スレッドが実現する。この製品の登場は来年前半とのこと。