Samsung 14LPP

TSMCに対抗するのはSamsung/GLOBALFOUNDRIESの14LPEと14LPPである。こちらはTSMCよりも若干立ち上がりが遅れつつも、第1世代である14LPEはやはりAppleのA9に採用されており、間もなくこれを改良した14LPPの量産が始まると思われる。

すでに複数のAMD製品が14LPP向けにTapeoutしたことがアナウンスされており、これは次世代CPUコア「Zen」と、場合によってはGPU製品も含まれている可能性がある。ちなみにこの製品がGLOBALFOUNDRIESだけでなくSamsungで生産される可能性があるといったニュースが昨今出ているが、そもそも両社は同一のプロセスを提供しているから、これは不思議でもなんでもない。

さて今回GLOBALFOUNDRIESは14LPE/14LPPに関するセッションは一切行っておらず、その代わりにSamsungが何回か14LPPに関するセッションを行ったので、この内容をご紹介したい。

以前の記事でも触れたように、14LPPは14LPEの高性能版という扱いであったが、どう高性能化したか? というのがこちら(Photo28)だ。

要するにFinの高さを引き上げる事で、より駆動電流を増やした形だ。このあたりは、Intelの22nm世代ではHigh-Speed Logic向けとSoC向けでFinの高さだけでなく幅も変えたことと対照的だ。ただ14nm世代ではそもそもFinが薄くなりがちで、高さを引き上げるのはそれなりに難しい筈だが、今回は流石にそのあたりの話はなかった。いずれこのあたりは学会あたりで何かしら発表があるかもしれない。

さてその14LPPを利用してSoCを製造するための最適化技法(DTCO)のスライドを何枚か紹介する。何度か言われてきたことだが、FinFETの世代ではゲートの幅などを微調整するといった技法は使えないため、基本的にはFinを何本構築するかという形による性能調整しかできない。そのため性能値は離散的な振る舞いになる(Photo29)。

|

Photo29:以前だと「ゲートの幅をちょっと増やす/減らす」なんて細工で性能調整が可能だったが、FinFET世代ではこれが一切不可能である。というのは、ちょっとFinの幅を変更するだけでえらく性能がブレるから。高さも同じで、これはエッチングの厚みそのもの変更になるから、製造プロセス全体に影響する。なのでFinの高さと幅はファウンダリが定めたものしか利用できない |

問題は14LPE→14LPPでは、そのまま高さが増える形になるので、例えば14LPEだったら3Finが必要だったところが14LPPでは2Finで済むといった事も起こりえる。なので設計をやり直すのであれば、よりエリアサイズが縮小できる場合もある。

またSRAMに関しては、これもFinFETの寸法をいじれない関係で、それほど構成が取れず、性能に関するパラメータが限られるという制約があるが(Photo31)、これに関しても14LPE→14LPPで安定性を増す方向に特性が変わるとしている(Photo32)。

さてここからはその14LPPのもう少し詳細だが、14LPEでは9TrackでCPP(Contacted Poly Pitch)は78nmのみが提供されたのに対し、14LPPでは10.5TrackのCell Libraryが提供され、またCPPには78nm以外に84nmも提供されるようになった(Photo33)。

Samsungはそれぞれを次のように分類している(Photo34)。

- 9T/78CPP:High-density

- 9T/84CPP:High-Performance

- 10.5T/84CPP:Ultra High-Performance

|

Photo34:CPPを78nm→84nmにすると理論上はエリアサイズが8%ほど増える計算になる。Mobile向けSoCにはこれはきついが、GPU向けならそれほどでもない。そして9Tと10.5Tにするとやはり16%ほどエリアサイズが増える計算になるから、これはGPUにもきついが、その分高速化しやすいので、CPUなどには最適だろう |

ただ、一般的に言えば

- スマートフォンなどのSoC向け:High-density

- GPUなどの高密度/高性能向け:High-Performance

- CPUなどの高性能向け:Ultra High-Performance

といった使い分けになるかと思われる。

ちなみに78CPPと84CPPでは、必ずしも78CPPが小さくなるとは限らないという説明がこちら(Photo35,36)。そのため、実際には78CPPと84CPPのエリアサイズの差は、もう少し小さくなる可能性がある。

最後に、これはSamsungではなくSynopsysの講演であるが、16コアのCortex-A53を集約したNetwork向けのSoCを構築した場合のトライアルの結果が簡単に触れられていた。曰く、9Track Libraryを使ってのQuad Core Cortex-A53のCPU Clusterのインプリメントはおよそ4週間で可能だったとの事(Photo37)。

|

Photo37:このSoCはQuad Core Cortex-A53のClusterを4つ、CCN-502に繋ぐという壮絶な構成になっている。注意したいのは4週間で可能なのはSoC全体ではなく、CPU Clusterを作るだけという点だ。0.72V動作だと1.44GH動作、0.8Vまで上げると1.7GHzまで引っ張れた |

これを9Trackのままと10.5Trackに移植して最適化を行った結果がこちら(Photo38)。10.5Trackだと電圧を変えずに4%ほどの性能改善が可能になったが、エリアサイズでは1割ほど増えているという試算になっている。

|

Photo38:「たったの4%?」と思われるかもしれないが、もともとが高速向けではなく省電力向けのCortex-A53コアなわけで、同じことをCortex-A57/A72などでやればまた違う結果になると思われる。もっともそのあたりを明確にしたくないからCortex-A53でやったのかもしれないが |

GLOBALFOUNDRIES 22FDX

2015年7月、GLOBALFOUNDRIESは22nm FD-SOIを提供することを発表したが、今回はこの22FDXに関する詳細のセッションがあった。

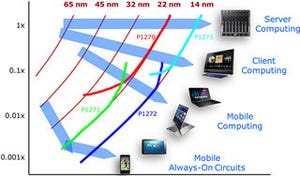

まずFD-SOIの位置付けがこちら(Photo39)。2015年7月の説明でも14nm FinFETを補完する位置付けとあったが、実際に22FDxは28SLPと同等のコストで、14LPPよりやや遅い程度の性能を提供できるとする。

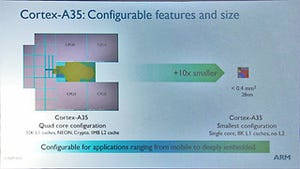

その22FDXであるが、ベースとなるライブラリはinvecasが提供する8 TrackのCell Libraryで、Power ManagementやCacheなどに関してはGLOBALFOUNDRIESからライブラリやマクロが提供される形だ。今回の発表はこれを利用して、Quad CoreのCortex-A17を実装したという話である(Photo41)。Floor Planは28SLPのケースと余り変わらない(Photo42)そうである。

|

Photo42:ただし"Very similar"というほど似ていない気がする。ちなみに28SLPの方の色分けは22FDXと違っており、Data Engine→紫、Core→水色、ISide→赤、DSide→緑と思われる |

さて、問題のBody Bias。Lower LayerにBody Bias用の電源層を1層追加し、ここから各トランジスタにBias電圧を供給する形となる(Photo43)。で、本来のトランジスタの駆動電圧よりもずっと電圧が高い関係で、このBody Bias用のネットワークの間隔は広めに取らないとまずいとの話であった(Photo44)。

では実際にBody Biasを使うと特性がどうなるか? というのがPhoto45である。FBB(順方向ボディバイアス)を使うと、スイッチング速度が上がるので動作周波数を引き上げ可能で、逆にRBB(逆方向ボディバイアス)を掛けるとリークが減るので省電力に向いている。

具体的には、同じ消費電力なら30%性能アップ、同じ動作周波数なら45%の消費電力ダウンが期待できる(Photo46)ということで、さらに配線も22nm相当にシュリンクされるから、エリアサイズも削減できる。実際FD-SOIウェハのコストアップ、あるいはBody Biasを実装するためのコストアップは、このエリアサイズ削減で相殺できるというのが同社の主張である。

もっともこれに関しては、現時点では少なくともDesign Inしたというアナウンスは皆無である。一応Cadenceはこの22FDXに対応したEDAのToolchainを提供するとしており、設計フローはBulk CMOSとほぼ同等とGLOBALFOUNDRIESは説明してはいるが、それをそのまま字義通り受け止めるユーザーは居ない、ということだろうか。

ということで、ARM TechConに絡む形で最近の先端プロセスの動向をご紹介した。これが実際の製品にどう反映されてゆくか、という話は(恒例の)新年特集でも触れる予定だ。