AMDのここ数年の躍進から注目を集めるようになったチップレット。先端プロセスで製造するSoC(System on Chip)の今後の進化の方向として重要な役割を担うと目されている。そのダイ間インターコネクトの標準を策定し、チップレットのオープンなエコシステム構築を目指すコンソーシアムが結成された。PCI-Expressの成功に倣った取り組みになっており、設立メンバー企業は、Advanced Semiconductor Engineering(ASE)、AMD、Arm、Google Cloud、Intel、Meta、Microsoft、Qualcomm、Samsung、Taiwan Semiconductor Manufacturing Company(TSMC)など10社。チップ設計やシリコンIPプロバイダー、ファウンドリ、クラウドサービスプロバイダーなど、関連する幅広い産業から参加を得た。

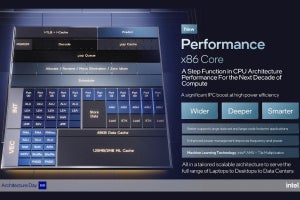

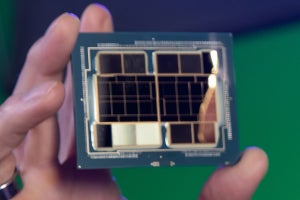

チップレット・アーキテクチャは、全回路を単一のチップに集積するのではなく、小さなチップレットを組み合わせて全回路を構成する。CPUには最先端のプロセス、I/Oコントローラには古い世代のプロセスというように回路ごとに最適なプロセスを採用できる。また、大きく複雑なチップに比べて小さなチップレットは歩留まりが良く、コスト削減を見込め、市場投入までの時間を短縮できるといったメリットがある。

しかし、チップレット(ダイ)間の接続が標準化されていないと独自のインターコネクトが林立する断片化した市場になってしまう。相互運用可能なマルチベンダーのエコシステムを構築することで、デザインコストを引き下げられ、企業間の連係による多彩なソリューションの可能性が広がる。

新コンソーシアムによるチップレットのオープン仕様は「Universal Chiplet Interconnect Express (UCIe) 」と呼ばれており、3月2日からUSIeのサイトにおいてメンバーへの1.0仕様の提供が始まった。AnandTechによると、ダイ間I/Oの物理層やプロトコル、ソフトウェアスタックをカバーする同仕様は、Intelが提供した技術を土台としている。現在、オープン標準組織として法人化の最終手続きを行っており、完了後にチップレットのフォームファクタ、管理、セキュリティ、他の基本プロトコルの定義など、次世代のUCIe技術に向けた作業を開始するとしている。