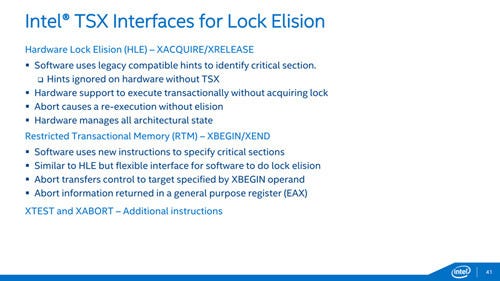

またHaswell世代からIntel TSXというトランザクションメモリ命令が追加されている。この詳細は安藤先生のこちらの記事をお読みいただくとして、実際にはHaswellの世代では問題が見つかっており、Haswell-EPでは「実装はしているものの、無効化」状態となった。

この話はHaswell-EPの発表時でも触れている。この時の話では、Haswell-EX世代でTSXを修正するという話だったが、BroadwellコアではこのTSX命令が高速化されると共に新命令が追加されたとしている(Photo14)。

|

Photo14:ただこの新命令を含むTSX命令が「問題が修正されて有効化されているのか、それとも新命令は追加されているがまだ修正は終わっておらず無効化されているのか」については問い合わせを行ったがまだ返事が来ていない |

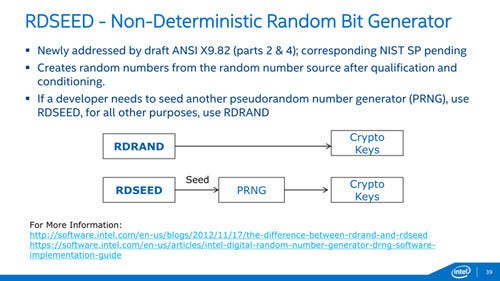

このほか、コアの新機能としては、以前から話題になっていたRDSEED命令が実装されている(Photo15)。これが何か? についてはIntel Developer Zoneのblog記事が詳しいが、NIST(米国立標準技術研究所)がSP 800-9B & Cという形で新しい乱数発生メカニズムの標準を制定(ただしドラフト)しており、これに対応したものである。

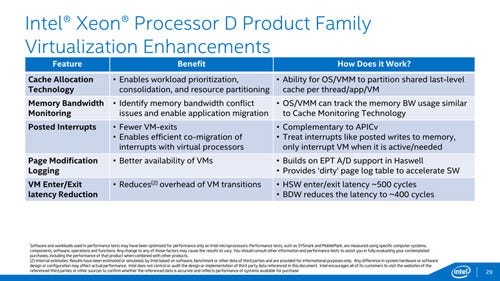

他に、仮想化周りとしてはこんな点が改善点として挙げられている(Photo16)。

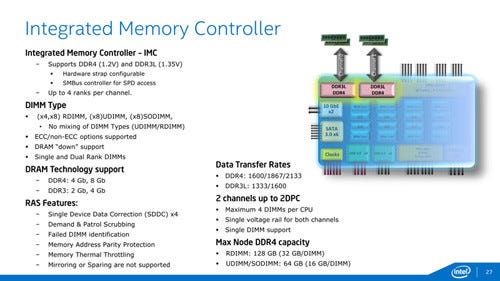

メモリコントローラの詳細はこちら(Photo17)で、1.5VのDDR3のサポートそのものは省かれ、DDR3LとDDR4のみのサポートになった模様だ。チャネルあたりDIMMは最大2枚までで、8Gbit DDR4チップを使った構成ではDIMMあたり32GB、最大で128GBという計算である。

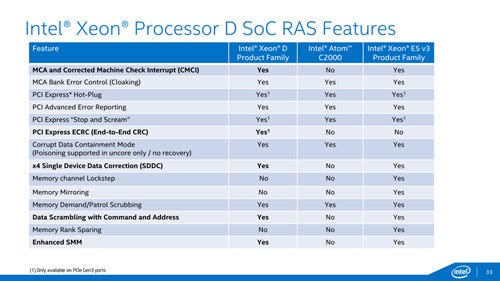

先ほどPhoto06でHigh Availability Memory Controllerとあったが、その"High Availability"はRAS機能のところに集中しており、ECCのサポートやThermal Throttlingといった機能が追加されていることを指すと思われる。

具体的なXeon DファミリーのRAS機能の一覧はこちら(Photo18)で、なにしろMemory Channelが2chしかサポートされていないので、4chのMemoryを持つXeon E5 v3シリーズの持つMemoru Channel Lockstep/Mirroring/Rank Sparingといった機能は搭載されないが、それ以外はほぼXeon E5と同等のRAS機能を搭載している事が分かる。

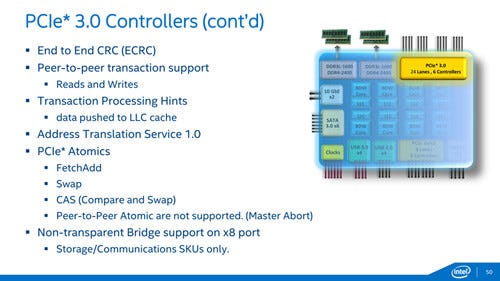

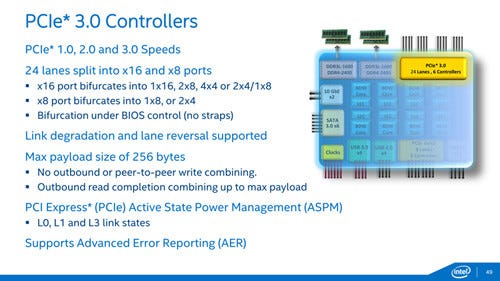

PCIe周りで言えば、そもそもXeon D1500はIIO側にPCIe 3.0 x24レーンを、PCH側にPCIe 2.0 x8レーンを搭載する。そのPCIe 3.0側は24レーンに対して6つのControllerを搭載しており、さまざまな構成が可能となっている(Photo19)ほか、Intelとしては初めてECRCや、ついにTransaction Processing Hint、あるいはAtomicをサポートするものとなった(Photo20)。

|

Photo19:Xeon D1500のPCIe 3.0は、主にRAIDコントローラや高速なNetwork Card(Infinibandや10/40GbEカード)、あるいはXeon Phiなどのアクセラレータを装着するためのものとなる |

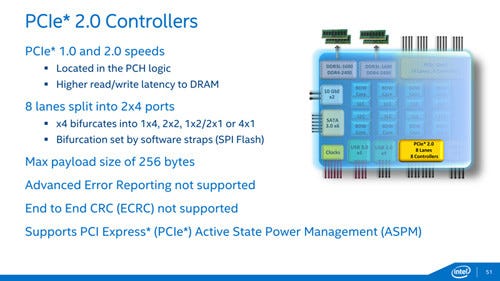

このあたりは、いずれ出てくるBroadwell-EPベースのXeonにも引き継がれることになるだろう。一方PCIe 2.0の方は従来のPCHのものと同じであり(Photo21)、こちらはオンボードデバイス類を接続するためのものと思われる。

|

Photo21:注意書きにもあるとおり、こちらに接続したデバイスをアクセスするためのLatencyはかなり大きいため、アクセラレータを接続したりするのには全然向いていない。またECECも未サポートであり、オンボードで追加のSATAコントローラやUSBコントローラなどを追加するのが主要な目的だろう |

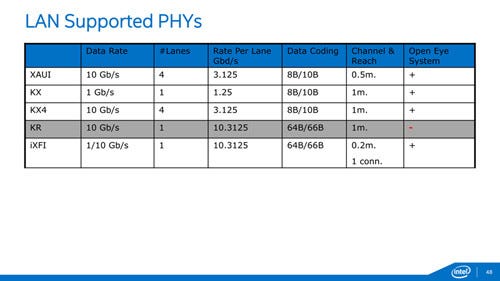

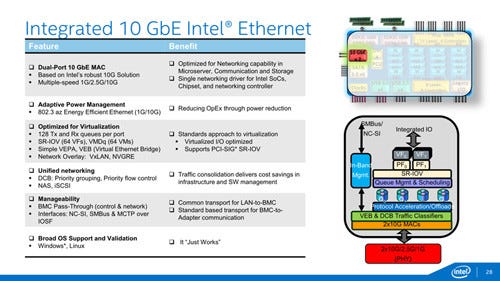

最後の10 GbEについて。IntelはすでにDiscrete製品として、さまざまな接続方法に対応した10GbEカードをX520/X540シリーズとしてリリースしている。

ただ表を見ていただくとわかるが、コントローラそのものはIntel 82559EBないしIntel 82559ESで、そこにPHYをメディアにあわせて外付けする形になっており、Xeon DではこのIntel 82559相当の機能をオンチップで搭載したような形になっている(Photo22)。

|

Photo22:機能的にはほぼIntel 82559と同等。消費電力は82599ES/82599EBの場合、Dual Portで2.7W~5.2W(メディアによって変化)だが、Intel 82559自身は65nmプロセスで製造されているので、14nmプロセスを使うXeon Dでは10GbE MAC部の消費電力は1W未満に収まるだろう |

I/FとしてはXAUI/KRなどをサポートしており、あとはPHYを選べばさまざまな10GbEを利用できると思う(Photo23)。ただ先のPhoto06を見ると、バックプレーン接続用の10GBase-KRとか10GBase-KX4しか考慮していないあたりがちょっと不便な気がするのだが、例えば10GBASE-T用のIntelのPHYは接続できるか? を確認したものの返事をいただけていない。まぁ3rd Partyの10GBASE-T用XAUI PHYはいろいろあるので問題はないのかもしれないが。