内部構造 - Broadwellコアの詳細についても公開

さて、ここからはもう少し内部構造について紹介したいと思う。実はこれまでIntelはBroadwellコアそのものについて、あまり内部構造を明らかにしてこなかった。Xeon Dシリーズの発表によって初公開となる情報もいくつか含まれており、ちょっと興味深い。

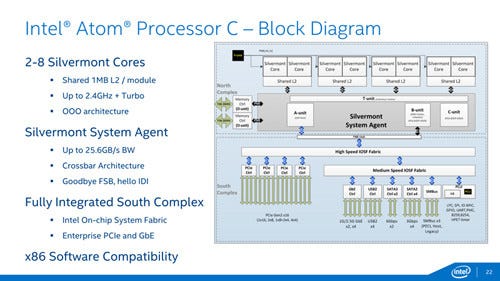

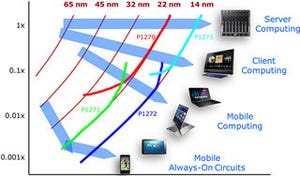

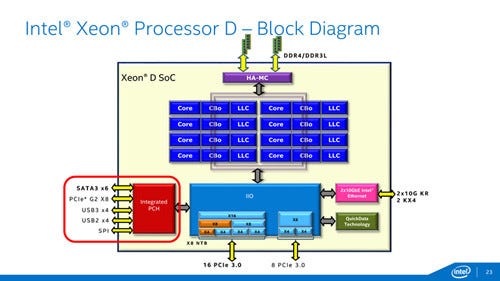

まずはSoC全体の構造である。Photo05がAtom C2000シリーズ、Photo06がXeon D1500シリーズの内部構造である。Atom C2000はどちらかというとARM系SoCによく見られるFabricをベースとした構造で、一方Xeon Dの方はSandy Bridge以降のCore iシリーズの構造をそのまま踏襲したような構成になっているのがわかる。

|

Photo06:新たにIIOと呼ばれる高速I/O Hubが追加され、ここにPCIe Gen3と10GbEコントローラ、及びIntel QuickData TechnologyへのInterconnectがぶら下る。従来のPCHはそこから更にぶら下る形 |

CPUコアはいずれも1.5MBのLLCをもち、これが2重のRing Busでつながる構成で、このあたりはHaswell-EPの4~8コア構成に同じと思ってよい。ちなみにメモリコントローラのHA-MCは"High Availability"の略の様だ。

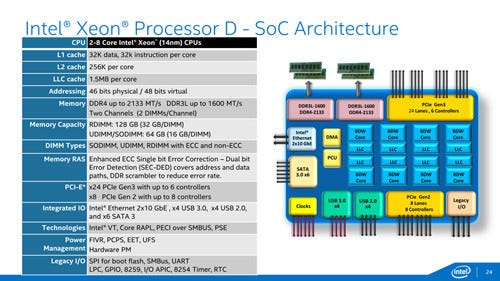

スペック的にはこんな感じ(Photo07)で、PCIe Gen3レーンが24本、USB 3.0×4、SATA 3.0×6、10GbE×2とエントリサーバーにしてはかなり豪華な構成である。

|

Photo07:動作周波数が2GHz(Xeon D1540)あるいは2.2GHz(D1520)と低い事とGraphicsを統合しない以外はHigh-End Desktop向けとしても結構使えそうなほど豪華な構成であり、実際そういう製品も登場するかもしれない |

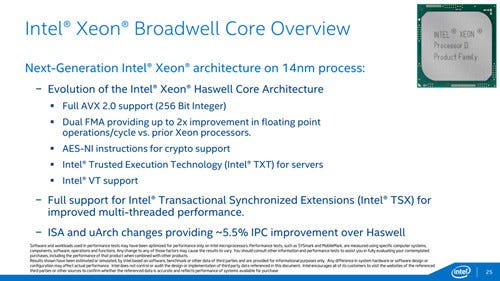

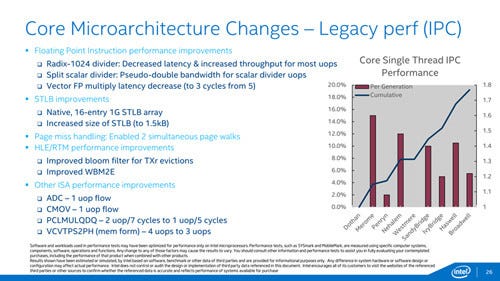

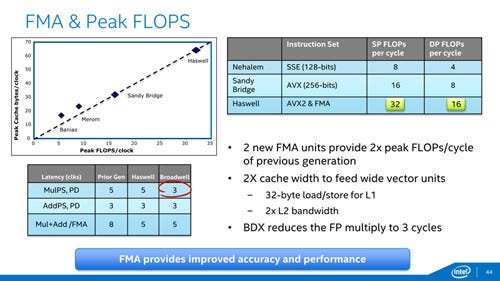

Broadwellコアそのものだが、IPCにしてHaswellに比べて5.5%ほどの改善がなされるとしている(Photo08)。Photo09がその内訳であるが、FPU性能のいくつかの改善、Second TLBの容量拡張、TSX命令の性能改善、およびいくつかの命令の性能改善が主なところである。

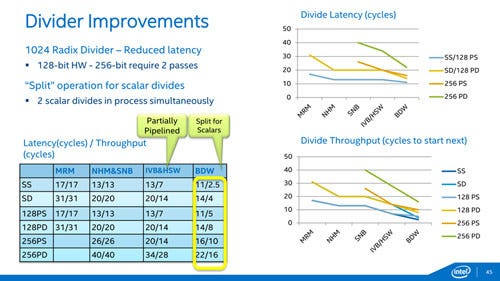

まずFPU命令については、単精度/倍精度の加乗算のLatencyがほぼ半減しており、スループットそのものはHaswellと変わらないものの、実効性能が改善している形だ(Photo10)。また除算に関してはHaswellから大幅に高速化されており、Throughput/Latencyの両方が高速化されているのが分かる(Photo11)。

|

Photo10:HaswellのFMA周りの話は安藤先生のこちらの記事を参照。右の「2つの新しいFMAユニット云々」の言及やL2のBandwidthの倍増はBroadwellではなくHaswellの話と思われ、Broadwell特有の話は左下の表、それとFPの乗算が3cycleに高速化された事のみと思われる |

|

Photo11:BroadwellではScalae除算を完全にパイプラインを分離したことで、同時に2つの除算が可能になった。また、IvyBridge/HaswellではRadix-16 DividerだったのをRadix-1024に切り替えた。これらにによって、浮動小数点演算に関しては明確に性能改善がもたらされた |

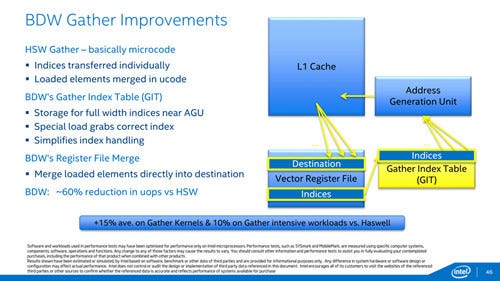

さらにGather演算(不連続なメモリエリアのアクセス:詳細は安藤先生のこちらの記事を参照)を、従来のMicrocodeベースのアクセスからGIT(Gather Index Table)ベースに切り替えることで高速化できたとしている(Photo12)。これは特にSSE/AVX命令を使って行列演算などを多用する場合には効果的であろう。

|

Photo12:AGU(Address Genration Unit)に対して、次にアクセスすべきアドレスをGITに格納しておき連続してアクセスできるようにすることで、必要となるMicroOpを60%近く節約し、カーネル処理で15%、アプリケーションで10%のワークロードを節約できるとする |

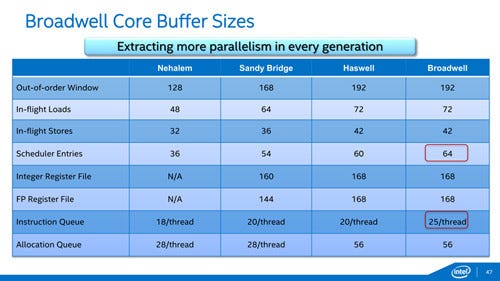

また実行パイプライン内部のバッファも若干増量されており、より効率を高める様に工夫されているそうだ(Photo13)。

|

Photo13:Scheduler EntriesとInstruction Queueがそれぞれ増加されており、これはExecution Unitの利用効率を更に高めるのに効果的と思われる。ただOut-of-order WindowsとかRegister Fileなどが強化されていないのは、現在のFront Endではこれを強化しても効果ないためと思われる。これを見ると、やはりここの最後で書いたように、SkylakeではFrontendの拡張が待っているように思われる |