消費電力の話も出たついでに、省電力周りの話も少し。これは専らMobile向け、特にHaswellで投入されるSoCを意識した話である。ちなみにHaswell世代では、遂にPCHを統合した1チップのSolutionが出てくるが、残念ながらこれは1つのダイの上にCPU/GPUコアとPCHが乗ったものではなく、MCMを利用してCPU/GPUのダイとPCHのダイの2つがワンパッケージになった、SoCというよりはSiP(System in Package)と呼ぶ方が正確なものである。まぁそれはともかく。

|

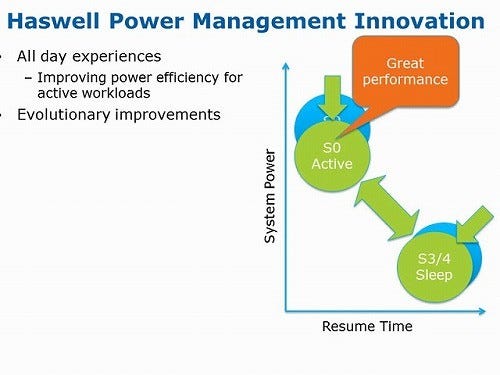

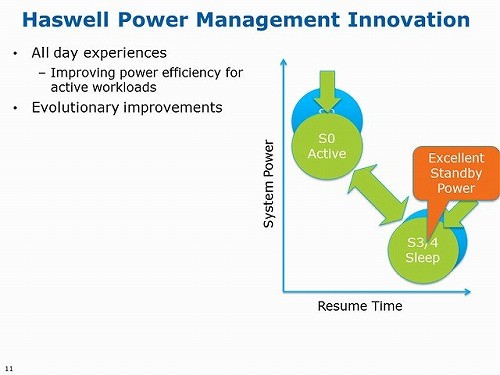

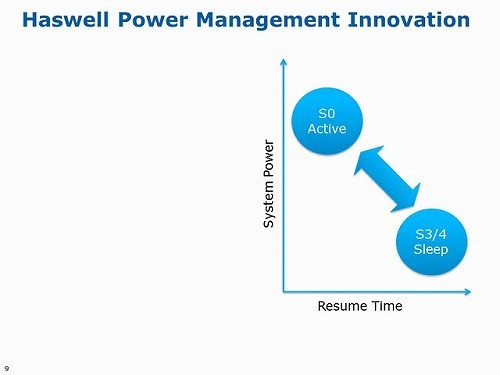

Photo06: これはベースラインとなるIvy Bridgeでの話。S0モードは消費電力は多いがResumeは短い(というか、0)。S3/S4は消費電力を下げているが、Resumeまでに時間が掛かる。 |

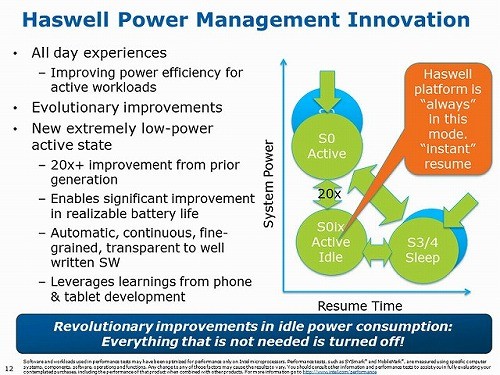

先ほどのPhoto02にもちらっと出てくるが、基本的にHaswellはIvy Bridgeと同じ22nmプロセスで、プロセスそのものの省電力化という観点ではIvy Bridgeと変わらない(Photo06)。ただ、Clock GatingとPower Gatingをより細かく行うようにしたことで、若干の消費電力削減に成功している(Photo07,08)。今回の特徴は、これに比べて新しくS0iX(X:1/3)というモードが追加されている事だ。実はこのS0iX、Haswellが初めてではなくEmbedded向けのAtom Z600シリーズで初めて投入されたStateである。

Atom Z600はIntelとしては初のSoCであるが(こちらはなんちゃってSoCではなく、本当にSoC)、こちらでは、

S0i1: CPUはC6 State、SRAMとWakeup Logic、Power ManagementはOn。Memory ControllerはSelf Refresh。DisplayはOff。その他のコンポーネントはPower Gated。

S0i3: Memory ControllerがSelf Refreshで、それ以外は全部Off。

という構成になっている。レイテンシは? というと、

| S0→S0iX | S0iX→S0 | |

|---|---|---|

| S0i1 | 600μs | 1.2ms |

| S0i3 | 480μs | 3.1ms |

といった数字が示されている。

何でこんなモードがあるかというと、Atom Z600の場合は「CPUコアは停止させつつ、周辺機器は動かす」という使い方があるためだ。組み込み機器の場合、「周辺回路から何かイベントが発生して処理が必要になるまで、CPUは寝ている」というケースは珍しくない。もっと言えば、例えば周辺機器でイベントが発生した場合、勝手にDMAを行ってデータを取り込み終わってからおもむろにCPUに割り込みを発生させるとか、下手をすると完全に処理を周辺回路でオフロードしてしまってCPUを起こさないなんてケースもあり、そんなわけでCPUにはとにかく寝ててほしい(が周辺回路はちゃんと動かないとまずい)場合が多い。ところがここでS3とかS4を使うと、周辺回路も一緒に寝てしまうことになり都合が悪い。そこでCPUコアは寝てるけど周辺回路は起きているというステートが必要になり、これがS0iXとして投入されたわけだ。

これがHaswellに搭載されたのは、PCHをSiPの形で統合することに関係する。つまりCPUコアは寝ていつつ、PCHコアには仕事をしてもらう必要があるわけで、このケースがS0iXとして定義された訳だ(Photo09)。待機電力を20分の1にする、というのはこの状態を追加することで実現した形になる。

ちなみにその他の工夫として、遂にRing Busが独立して動作するようになった。また周辺回路も大幅に手が入れられており、システム全体としての消費電力の削減に関しても随分工夫されている(Photo10)。

ということでここまでで随分長くなってしまったので、AVX及びTSXについては次の原稿に回したい。

編集部追記:

AVX及びTSXについて、続報記事となる、

「【レポート】IDF 2012 - 次期Intel Core「Haswell」の内部構造を探る - 拡張命令(AVX2/TSX)編」を掲載しました。

http://news.mynavi.jp/articles/2012/09/18/idf03/