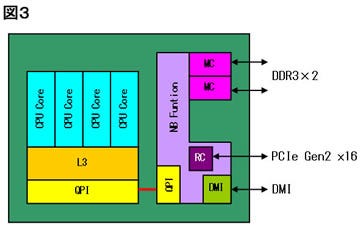

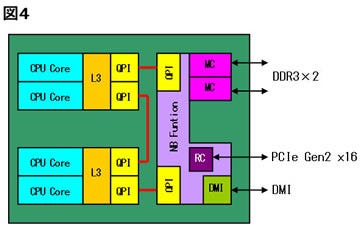

さて、Clarkdale/Arrendaleが図2の構成だとすると、ではLynnfield/Clarksfieldがどんな構造になるのか? というのが次の疑問だ。当初、筆者は図3か図4の様な構造を考えていた。当時はまだClarkdale/ArrendaleのCPUコアがWestmereベースになるという話はなかったから、そうなると例えば図4の様な構成にすればClarkdale/Arrendaleと同じCPUのダイを使えることになる。ただ、3チップMCUというのはちょっと難易度が高すぎるので、現実的には図3の様な構造ではないか? と想像していた。

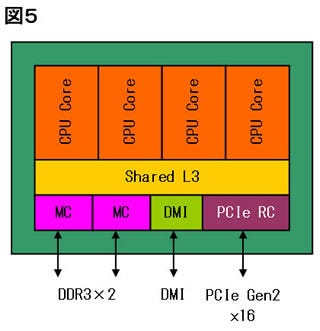

この想像が一気に覆されたのが、先に書いた電話会議である。筆者の質問に対してSmith氏はハッキリと「LynnfieldはMonolithic dieで構成される」と断言した。つまり、MCMではないということだ。となると、内部構成は図5の様な形になるのが現実的だと考えられる。

Monolithic dieならば、無理にMemory ControllerやPCIe Gen2のFunctionを分離して、QPIで繋ぐ必要が無い。普通にMemory ControllerやDMI/PCI ExpressのRoot ComplexがShared L3の下にぶら下がっている構造を考えるのが普通だろう。ちょっと意外だったのは、同じ45nmプロセスで、しかも4コアでありながら異なるI/Fを持つCPUコアを2種類作る事だ。とはいえ、Nehalem/Nehalem-EPは先の図1の様にDMIやPCIeを持たないから、これをそのまま流用するわけには行かないので、やむを得ない決断か……と考えていた。