Core i5/i3 Update

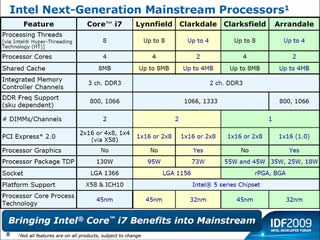

では一般ユーザー向けでは何も情報が無いのか、というとそういうわけでもなく、ちょっとではあるが情報があった。まずPhoto05は"The Platform Evolves: Understanding the Intel Next Generation Microarchitectures (Nehalem and Westmere)"というタイトルのセッションのプレゼンテーションからの抜粋である。

|

Photo05: ArrendaleのPCI ExpressがGen1相当に限られるのは、別にシリコンが異なるのではなく、省電力のために2.5GHzでしか動作しないようにパラメータで変更を掛けているだけであろう。 |

ノート向けのClasksfield/Arrendaleが省パッケージで、消費電力も18W~55Wの枠に収まっているのは、まぁ用途を考えれば当然と言える。グラフィック統合のClaskdaleとArrendaleがコア数が2であるのも、既報の通り。目新しい事柄としては、

- デスクトップのパッケージはLGA1156となる(既に広く知られているとは言え、公式にはまだ未公開だった)。

- Processing Threadsが"Up to 8 or 4"という表記であり、これは要するにHyper-Threadingを有効に出来るSkewと、無効にされるSkewが存在する。

- 同様にL3キャッシュについても、"Up to 8MB or 4MB"という表記であり、例えばLynnfieldであれば8MBの構成と(おそらくは)4MBの構成の両方がある。

といったあたりだろうか。

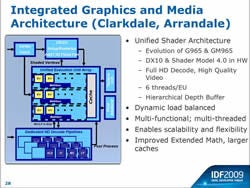

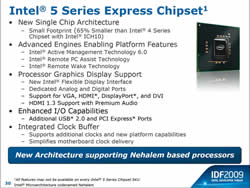

その他新しい情報としては、Clarkdake/Arrandaleに搭載されるGraphicsの概略(Photo06)とかチップセットの概略(Photo07)などが公開されたが、情報はこの程度で極めて限定的である。実のところ、IDFの翌週にXFASTESTが5日付のNDA Roadmapを掲載しており、まぁ信憑性は各自で判断していただくとして、とりあえず概ねIDFで示された内容と矛盾はないようだ。ということで、以上、終わり……というのも何なのでもう少し。