省電力機構

今回いろんな意味で一番インパクトがあったのがこの省電力機構である。今回明らかにされた省電力機構は大きく2つある。これを順に説明しよう。

●Power Gate

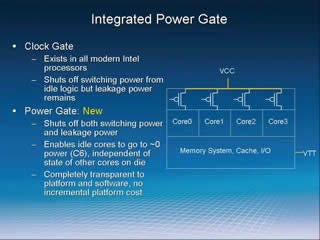

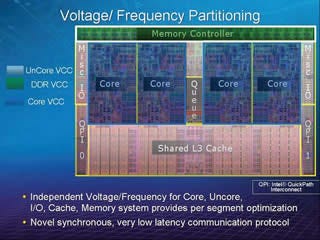

Nehalemでは内部の回路が大きく3つに分類される(Photo12)。

|

Photo12:厳密に言えばQPIやMISC I/OはUncoreには入らない(L3などとは電圧が異なるし、QPIなどは独自に電力管理をやっている様なので、このあたりは複雑になっている)が、CPUから見た場合にはこれらはUncoreと一緒に除外して考えられる、という意味。 |

具体的には、

- Core : CPUコア+L1/L2キャッシュ

- Uncore : L3キャッシュ、QPIとその他のI/O I/F

- Memory : DDR3のメモリコントローラ

が独自の電圧プレーンとして設定されている。

これらを個別に電圧設定する、という話は例えばAMDがK10で実装したSplit Power Planeに近いもので、技術的にもそれほど珍しくはない。大きく異なるのは、各コアに供給されるVCCにスイッチを入れる事で、待機状態のコアへの電力供給を文字通りカットしてしまった事だ(Photo13)。勿論、電気回路的には極めてシンプルである。要するにVccと実際の回路の間にスイッチングトランジスタを入れてやれば済む話だ。ただし実際にはこうした実装がこれまで行われなかったのは、

- 扱うべき電流が大きすぎる。スイッチだから、コアのフル稼働時にはTDP上限の130Wとか150W(Xeonの場合)が流れる。コア電圧1.5Vとすると100Aである。コア4つでこれを均等に分けるとして、コアあたり25Aにも達する計算だ。これだけの電流を制御するのは大変である。

- CMOSを使わなければならない。半導体ならなんでもいい、という話であればIGBT(絶縁ゲートバイポーラトランジスタ)を使えば話は簡単だ。IGBTならば400V/200Aなんていう高電圧・高電流に耐える製品が普通に入手できる。しかしながら、製造プロセスが全く違うだけに、CPUコアに埋め込む訳にはいかない。しかも、CPUコアと同じプロセスで製造する必要がある。当然ながらこんなトランジスタはそんな高耐圧ではない。

というあたりがネックになっていた。

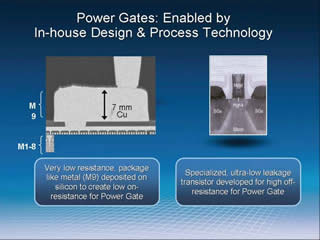

これに対するIntelの答えがこちらだ(Photo14)。まず回路と配線層1~8を通常の方法で作成する。ついで、その上にインターポーザー経由で7mmもの厚さを持つ電力配線層を追加した上で、スイッチング専用のトランジスタを開発してこれに対応した、としている。

それにしても、である。UncoreやらMemory Controllerの分を除いて少なめに見積もってもコアあたり20A程度のハンドリングは必要であろうから、これを1つのトランジスタでスイッチするのは不可能だろう。数百のオーダーでも無理で、おそらくは数千~数万個のオーダーのスイッチを並列にする形で実装しているものと思われるが、これらを同期してOn/Offするのは更に大変に思える。

更に度肝を抜くのが7mmもの厚さのM9(9層目の配線層)である。途中にインターポーザーがかなり厚く挟まっていることから、これは通常の前工程が終わった後で貼り付けているとしか考えられない。"In-house Design & Process Technology"と言うが、たしかに外部のファウンダリを使っていたら、こんな実装は他では不可能だろう。ちなみに、一体スイッチングトランジスタはどこに配されているのかと思ったら(M8とM9の間か、と最初は思った)M1の更に下、つまり回路の中にそのまま埋め込まれているそうである。

PowerGateに関する詳細はここまでで、更に細かい話は今回は無かったが、今後Many Coreに次第に進化してゆくなかで、今回の技術はかなり重要なものに見える。いずれどこかでもう少し詳細が明かされることを期待したいところだ。

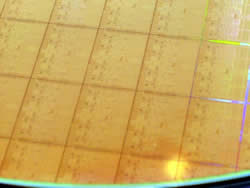

余談ながらそんな訳で、Nehalemのウェハ表面には7mm厚の銅配線が張り付いているわけで、従来と異なりウェハ表面は均一に光を反射しやすい。結果、撮影してもあまり面白みの無いものだった(Photo15,16)。

|

|

Photo15:この角度だと、室内の照明の関係か、わかりやすく見えるのだが。 |

Photo16:近寄って撮影するとこの有様。Intelがプレゼンテーションに使っているダイ写真はM9配線前のものではないかと思われる。 |

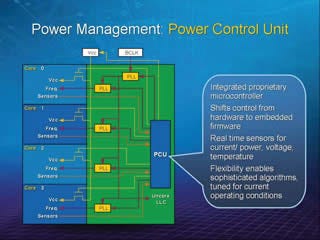

ちなみにPowerGateを含む制御は、Uncore側に設けられたPCU(Power Control Unit)が行っている(Photo17)。