Haswellを評価する

既報の通り、Intelは6月4日に、Haswellとして知られる第4世代Intel CoreプロセッサファミリーとIntel 8シリーズチップセットを正式に発表する(Photo01)。これにあわせて、Desktop向けのHaswellをあらかじめ評価する機会にも恵まれたので、レポートをお届けしたい。

■2013年6月21日追記: 追加検証を実施しました

【特集】「Haswell」完全攻略!! (追加検証) - 内部解析で第4世代Coreの真実にさらに迫る

http://news.mynavi.jp/special/2013/haswell2/

21プロセッサ、8チップセット

6月4日に発表される製品はかなり多い。現時点で公表されているだけで、

プロセッサ:デスクトップ向け14品種+モバイル向け7品種

チップセット:デスクトップ向け5品種+モバイル向け3品種

がある(Photo02)。このうちデスクトップ向けの14品種をまとめたのが表1である。ちなみに価格は1,000個発注時の1個あたりの金額であり、リテール品の店頭価格はおそらく6月4日の正式発表時に明らかになると思われる。ちなみに14品種といいながら、表1に12品種しかないのは、Core i5-4430/i5-4430Sについては未だに細かいスペックが示されてないためである。

| ■表1(Core i7) | |||||

| Processor Number | i7-4770T | i7-4770S | i7-4770 | i7-4770K | i7-4765T |

|---|---|---|---|---|---|

| Core/Thread | 4/8 | ||||

| Hyper-Threading | Yes | ||||

| CPU定格動作周波数(GHz) | 2.5 | 3.1 | 3.4 | 3.5 | 2.0 |

| CPU最大動作周波数(GHz) | 3.7 | 3.9 | 3.0 | ||

| 倍率アンロック | No | Yes | No | ||

| L3キャッシュ容量 | 8MB | ||||

| AVX対応 | Yes | ||||

| AES-NI対応 | Yes | ||||

| VT対応 | Yes | ||||

| 対応メモリ対応 | DDR3-1333/1600 | ||||

| 搭載GPU | Intel HD Graphics 4600 | ||||

| Intel Wireless Display対応 | Yes | ||||

| GPU最大動作周波数(MHz) | 1200 | 1250 | 1200 | ||

| QuickSyncVideo | Yes | ||||

| vPro/TXT/VT-d/SIPP対応 | Yes | No | Yes | ||

| PCI Express 3.0 | Yes | ||||

| パッケージ | LGA1150 | ||||

| TDP(W) | 45 | 65 | 84 | 35 | |

| Price($) | 303 | 339 | 303 | ||

| ■表1(Core i5) | |||||||

| Processor Number | i5-4670T | i5-4670S | i5-4670K | i5-4670 | i5-4570 | i5-4570S | i5-4570T |

|---|---|---|---|---|---|---|---|

| Core/Thread | 4/4 | 2/4 | |||||

| Hyper-Threading | No | Yes | |||||

| CPU定格動作周波数(GHz) | 2.3 | 3.1 | 3.4 | 3.2 | 2.9 | ||

| CPU最大動作周波数(GHz) | 3.3 | 3.8 | 3.6 | ||||

| 倍率アンロック | No | Yes | No | ||||

| L3キャッシュ容量 | 6MB | 4MB | |||||

| AVX対応 | Yes | ||||||

| AES-NI対応 | Yes | ||||||

| VT対応 | Yes | ||||||

| 対応メモリ対応 | DDR3-1333/1600 | ||||||

| 搭載GPU | Intel HD Graphics 4600 | ||||||

| Intel Wireless Display対応 | Yes | ||||||

| GPU最大動作周波数(MHz) | 1200 | 1150 | |||||

| QuickSyncVideo | Yes | ||||||

| vPro/TXT/VT-d/SIPP対応 | Yes | No | Yes | ||||

| PCI Express 3.0 | Yes | ||||||

| パッケージ | LGA1150 | ||||||

| TDP(W) | 45 | 65 | 84 | 65 | 35 | ||

| Price($) | 213 | 242 | 213 | 192 | |||

もっとも今回、事前情報は駄々漏れといって差し支えないレベルだった。昨年から細かいマイクロアーキテクチャは色々公開されていたし、今年4月26日の朝8時頃(太平洋時間)にIntelはFacebookにこんな画像を公式アカウントで公開。換算すると太平洋時間で6月3日の23時位、日本時間で6月4日の15時になる計算だ。一カ月も前に製品の発表時間を公開するというのは、同社のこれまでからするとかなり珍しい。もっともその後もこんな発表が行なわれてたりするので、もう正式発表もへったくりも無い気もするのだが、まぁそれはおいておこう。

まずCPU側からUpdateを紹介してゆく。HaswellはQuad Core版の場合トランジスタ14億個、ダイサイズは177平方mmである(Photo03)。ダイそのものもごらんの様にかなり長細くなっている(Photo04)。300mウェハ1枚からおおよそ350~360個ほどダイが取れる計算になる。Intelはウェハの製造コストを公表していないが、22nmといった先端プロセスの場合、ウェハ1枚あたりの製造コストはおおむね1万ドル程度といわれているので、ここから考えるとチップ1個あたりの原価はおおむね30ドル未満。後処理工程(ダイシング/テスト/パッケージング)まで含めて原価は40ドルを超える程度と試算できそうだ。

|

|

Photo04: Ivy Bridgeもかなり長細かったが、Haswellでは更に長細くなった印象。 |

Photo05: 数にばらつきがあるのは、ウェハ周辺部の部分、どっからどこまでが良品かがハッキリ確認できないため。ただ350個は確実に取れると思う。 |

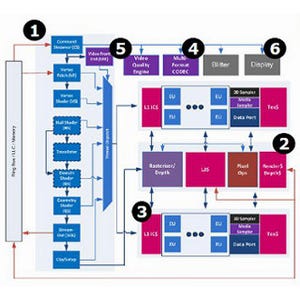

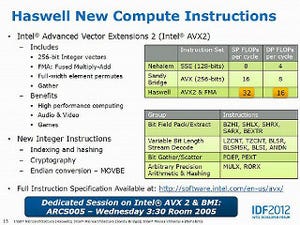

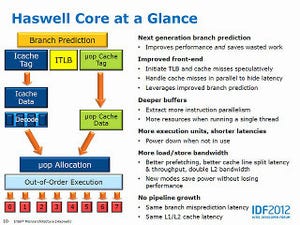

Haswellの内部構造については、昨年のIDFの解説記事(マイクロアーキテクチャ編、拡張命令(AVX2/TSX)編、Uncore(GPU/Media Block)編)で触れたのでここでは繰り返さない。ただ省電力に関しては幾つかの新情報があったので、これのみ説明しておきたい。

Haswellは、特にMobile向けに省電力を進めた点が大きな特徴の一つであり、U/Yシリーズはこれを推し進めた構造になっている(Photo06)。これを支える一つの技術が、新たなCステートのサポートである。CPUそのものはC0~C7までのステートを持ち、このC7ステートで事実上CPUは停止するのだが(Photo07)、システム的には更にC10までのステートが用意され、これを利用することでシステム的には更に消費電力を下げることが可能な用意がなされている(Photo08)。

|

Photo06: Haswell世代ではCPUに加えてPCHの電力も削減することで、トータルとしての消費電力を削減したという話。加えて言えばU/YはPhoto02にもあるように、1チップ構成となっており(要するにPCHをMCM構造で一つのパッケージに搭載した)、これも省電力に貢献している。この話は後述。 |

で、省電力の仕組みはこうしたものだけか、と思ったら「違っていた」というのが次の話。Intelは5月22日に電話会議でHaswellに関するブリーフィングを行なったのだが、ここでHaswellの利用する22nmプロセスの一端が明らかにされた。具体的に言えば、Haswellで利用されているのはP1270の拡張版のプロセスで、これにより性能を落とさずにリーク電流を2~3倍削減することに成功したとしている(Photo09)。この話を説明したのはKaizad Mistry氏(Vice President, Director of Logic Technology Integration)であるが、具体的にどうしたかまでは言えないとしながらも「FinFETを1年間製造してきたことで、ジオメトリに関して多くの知見を得た」と説明した。実は割とこれは重要な話である。FinFETは要するに3次元構造であるが、そのFinの幅とか高さに関しては、ちょっと変えるだけでものすごく特性が変わってしまうため、これを色々チューニングするのは大変に難しい。話は飛ぶが、GLOBALFOUNDRIESCが14XMプロセスでやはりFinFETを採用することを明らかにしており、既にCadenceやARMなど様々なベンダーがこのFinFET向けの設計ツールやIPなどを用意しているが、この14XMの場合Finの高さとか幅といったパラメータは一切変更不可能で、唯一Finの数を変更することだけが可能だそうだ。それだけFinの構造を変更するのはクリティカルという話なのであるが、Intelはこれを可能にしたという事らしい。もっともこれはP1270を変更したという話ではない(Photo09にも"Enhanced version"とあることでこれが判る)し、実際には回路の変更も伴うから、Ivy BridgeにこのEnhanced versionの22nmプロセスを適応できる訳では無いようだ。

またこの他の話として、回路自体にも見直しが入った(Photo10)ほか、新しい話としてFIVR(Fully Integrated Voltage Regulator)の実装がある(Photo11)。要するに電源レギュレータをオンチップで搭載したという話である。電源レギュレータにまつわる話はこちらでちょろっとだけ書いたが、話はもっとアグレッシブだった。

図1はIvy Bridgeにおける内部の電圧供給周りを大分簡略化して書いたものである。Ivy Bridgeの場合、5種類の電圧を外部から供給する必要がある。具体的には、

VCCIO:I/O用電圧

VDDR:DDR3-SDRAM用電圧

VCore:CPUコア用電圧

VAXG:GPU用電圧

VCCSA:System Agent用電圧

である。ただVCCIOやVDDRは動作周波数に関係なく一定なので、変化があるのはVCore/VAXG/VCCSAの3種類ということになる。従来、Power Gatingにより電圧のOn/OffはCPU内部に実装されたが、電圧の変化そのものは外部の電圧レギュレータで行なっていた。これが特に厄介なのは、たとえば4つのCPUコアのうち、一つだけがフル稼働、のこりの3コアが待機してるなんてケースだ。この場合、Activeなコアのみ電圧を上げ、残りの3コアはぎりぎりまで電圧を下げたいところだが、あいにくとCore用の電源レギュレータは共通なので、そういう柔軟な対応はできない。また、動作周波数にあわせて電圧を変化させる場合、CPU外部にリクエストを出し、それから電圧変化をさせることになるので、実際に電圧が変化するまでのLatencyが長くなるという欠点があった。

これがHaswellでは、図2の様に変更された。外部にも依然として電圧レギュレータは残るが、これは外部からくる12Vをいきなり内部の電圧レギュレータでCPUの要求に合わせてダイナミックに変更するのは負荷が掛かりすぎるためで、12VをまずVcc(Boot時は1.7V)に変更、ついで内部の各ユニットの要求に合わせて電圧を変更する形になる。ここで注目すべきは、コア毎にきちんと電圧レギュレータが別々に用意されていることで、これによりたとえばコア1はフル稼働ということで最大電圧、コア2~4は待機中なので最小電圧なんてことも可能になった。これは当然待機するコアの消費電力を下げることに役立つ。また必要とする回路のすぐそばに電圧レギュレータが置かれるので、電圧の変更を指示してから実際に電圧が変化するまでの時間の短縮も可能になる。これもまた省電力性の改善に役立つ訳だ。

もっともこれはいいことばかりではない。たとえばこれまでオーバークロック動作(特に液冷+電圧オーバー)を行なう場合、結果として猛烈な量の電流がCPUに流れ込む事になっており、これを支えるべくマザーボード側の電圧レギュレータも猛烈なものが用意されていた。10Phaseを超える電源レギュレータが用意されているマザーボードも結構珍しくなかったのだが、こうした製品は安定動作というよりは、むしろオーバークロック時の電力供給能力を確保する、というのが主要な目的だったわけだ。ところがHaswellの場合、マザーボード側の電圧レギュレータを強化しても、最終的には内蔵する電圧レギュレータがボトルネックになることになる。このため、オーバークロック動作で無理に高電圧を掛けたりすると、コアよりも先に電圧レギュレータが破壊することに繋がりかねない。

ちなみにIntelに確認したところ、この内蔵電圧レギュレータは常識的な範囲での電流供給が可能(オーバークロックまでは考えてない)であり、また放熱に関してもヒートスプレッダと接触させてそこから熱を逃がす的な配慮は特にしていないとの事だった。特に液体窒素とかを使ってのオーバークロックを考えておられる場合は、このあたりに注意してほしい。

次にチップセット周りだが、Photo12が基本的な仕様である。細かな仕様の違いは色々あるが、最大のものが一番上の"I/O Port Flexibility"であろう。Intel 7シリーズまで、たとえばUSB 3.0のポートはUSB 3.0しか使えなかったし、SATAはSATAのみ、PCI ExpressもPCI Expressのみであった。ところがたとえばUSB 3.0とPCI Express Gen2は同じPHYだし、SATAは速度こそ6Gbpsながら、Encodeは8b/10bだし電圧も同じだから、基本的には互換性が高い。そこで、汎用のPHYを用意しておき、これをUSBやPCI Express、SATAに自由に割り当てられるようにしたのがI/O Port Flexibilityである。といっても自作ユーザーにはあまり関係の無い話ではあるが、マザーボードを設計するときに「USB 3.0を6ポートにして、PCI Expressはその分減らして4レーンにしよう」なんて構成の変更が自由にできるようになる。具体的な製品としては、コンシューマ向けにはZ87(Photo13)とH87(Photo14)、ビジネス向けにはQ87(Photo15)、Q85(Photo16)とB85(Photo17)が用意される。

|

|

Photo14: PCI Express Gen3はx16レーン×1のみの構成だが、その分Anti-Theft TechnologyとかIdent Protection Technologyなど、ややビジネスよりの機能が追加されている。 |

Photo15: エンタープライズ向けということで、更にAMT 9.0とかStandard Managebikityなどが追加されている。 |

|

|

Photo16: Q87から、RAIDとかSRTの機能を省いた低価格版のQ85。 |

Photo17: ローエンドのB85。エンタープライズ向け、というよりは低価格向けとい扱いで、リモート管理周りの機能が大分省かれている。 |

ところで先ほど、U/Yシリーズでは省電力化に貢献するという話があったが、もう少しこれについて説明したい。既存のチップセットはCPUとDMI 2.0で接続される。これは基板やソケットを経由するから、それなりの電圧で信号を送信しないとノイズに負ける。このため当然ながらそれなりの消費電力となる。ところがU/YシリーズはCPUのパッケージ上で接続されるから、そもそも配線の絶対長がずっと短くなるし、ノイズの影響もずっと少ない。そこで信号の電圧レベルを下げても問題が無い。このため、U/Yシリーズに搭載されるPCHとCPUコアの間は、信号プロトコル的にはDMI 2.0のままながら信号レベルをずっと抑えたものが利用され、これによって消費電力を更に下げられるという話であった。

最後にチップセットに絡んでGPU周りを。Intelは新たにIrisというブランド名を導入したのは既報の通りだが、具体的なラインナップはこんな具合(Photo18)。上位モデルのIrisのハイエンドは、eDRAM(embedded DRAM)をオンチップに搭載した製品が用意される。ただしこれはデスクトップ向けではなくMobile向けのみである。このグラフィック周りの違いを示したのがこちら(Photo19)で、幾つかについては試してみる事になるだろう。

|

|

Photo18: ちなみに現時点のデスクトップ向けは、GT2のIntel HD 4600を搭載した製品のみがラインナップされている。 |

Photo19: チップセットというよりはCPU側の機能という事になる。 |

次ページ:今回のテスト機材の解説