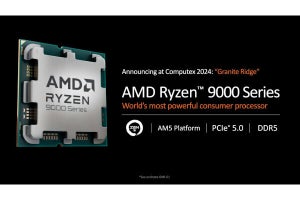

こちらではDiscreteのRyzen 9000シリーズ(と、ちょっとだけGen 5 EPYC)の説明を行ったので、もう一つの製品であるRyzen AI 300シリーズの方をご紹介したいと思う。といっても、まだStrix Pointの完全な内部構造の説明は無く(Photo01)、部分的な要素に関する説明と簡単なベンチマーク結果のみである(Photo02~04)。こちらの完全版は、評価キットにあわせて公開されるのではないかと思う。その一方で、RDNA 3.5の簡単な説明、それとXDNA 2の説明は行われたので、こちらをご紹介したいと思う。

-

Photo01: 内部構造の簡単な説明は以前こちらで示された通り。これ以上の話は今回出てこなかった。

-

Photo02: AI PC製品を全部並べて...といいたいところだが、IntelはまだLunar Lake搭載マシンが無いのでCore Ultra 185との比較。Snapdragon X EliteでPCMark 10が意外に低い理由、まさかとは思うがGame(3DMark Firestrike)のスコアを入れたPCMark 10 Extendedではなかろうか? Breakdownした結果が欲しいところ。

-

Photo04: 流石にSnapdragon X EluteでFar CryだF1 2022だを実行させるのは可哀そうだと思う。あとF1 2023でないのは、Ray Tracingを使わずに済むからかもしれない。

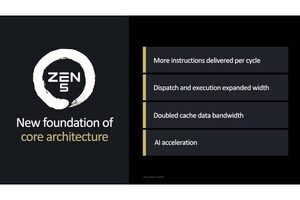

Zen 5+Zen 5C

Ryzen AI 300シリーズは、Hawk Point同様にZen 5とZen 5cのHybrid構成である。これに関してはAMDに確認し、

- The Ryzen AI 370 has 4 Zen 5 cores and 8 Zen 5c

- The Ryzen AI 365 has 4 Zen 5 cores and 6 Zen 5c

という返答を貰っているので間違いない。Photo00は以前AMDが示したRyzen AI 300の内部構造だが、よく見るとZen 5cのエリアとZen 5のエリアではCPU Coreの映像が異なっているのが判る。またShared L3に関しても、Zen 5の方は4coreにも拘わらずZen 5c×8coreの2倍になっている。

恐らくであるが、Zen 5cはZen 4cと同様に論理設計そのものはZen 5と同じで

- L3のサイズを1/4に減らしている

- 物理設計を、省電力/省エリアサイズ向けに振っている

という形でZen 5コアと違いを出しているものと考えられる。これにより、動作周波数が低いところではZen 5コアよりも省電力に動作する一方、動作周波数の上限は当然低いものになると考えられる。この辺の細かいプロファイルまでは今回説明されていない(今年のHotChipsあたりで何か出てくるといいのだが)。

RDNA 3.5

こちらの記事でも触れた様に、Ryzen AI 300に搭載されるRDNA 3.5ベースのGPUは、RDNA 3をよりIGPUに最適化した構成という話であった。その具体的な項目がこちら(Photo05)である。Texture SampleとInterpolation/Comparisonの性能を倍増というのは、要するにCU数が少ない時にはこれがボトルネックになりやすいので、それを補ったという意味だろうか? 一方でMemory Managementの管理は判りやすく、LPDDR5へのアクセスの最適化というのは、多分アクセス単位を16bitにしたというあたりではないかと思う。加えてメモリアクセスの方法を効率化すると共に、圧縮メカニズムの改良で、より少ないメモリ帯域で利用できる(=同じメモリ帯域なら、より性能を上げられる)様になったという事かと思われる。結果として同じ15W枠の中で、従来比で19~32%の性能向上が実現した、としている(Photo06)。

-

Photo06: とは言えHawk Pointは12CU構成だから、16CU構成のStrix Pointの方が性能を上げやすいのは事実ではあるのだが、ただIGPUの場合はメモリ帯域がボトルネックになってCUを増やしても性能改善に繋がりにくい事を考えれば、それなりに効果がある事は間違いなさそう。

XDNA 2

XDNA 2のベースとなるのが、今年4月に発表されたVersal AI Edge Gen2に搭載された第2世代AI Engineであるという話はこちらで触れた。これ、世代的には第3世代になる製品である。初代のAI EngineはVersal AI Coreに搭載されたものであり、これを改良してInferenceの性能を高めたのがVersal AI Edgeに搭載されたAI Engine-MLである。そのAI Engine-MLを改良したのがVersal AI Edge Gen2に搭載されたAI Engine-ML v2となる訳だが、基本的な構造は初代のAI EngineからAI Engine-ML v2まで違いが無く、VLIW-SIMD形式のAIE Tile(AI Engine Tile)とMemory Tile、それと外部との接続を担うNoC Shim Tileから構成される(Photo07)。異なるのはMem Tileの数とかAIE Tileの数、それとAIE Tileで扱えるデータ型などとなる。このAIE TileはMesh構造で接続され、AIE Tile同士はデータフロー的に動作する事が可能であり、また複数の領域にPartitioningして、それぞれ別のNetworkを動かすという事も可能である(Photo08)。ただ大規模なNetworkでは、時分割する形での利用も可能となっている(Photo09)。

内部構成がこちら(Photo10)で、AIE Tileが32に増強されているほか、いくつかの相違点がみられる。前世代、つまりPhoenix Point/Hawk Pointに搭載されたXDNAとの違いを示したのがこちら(Photo11)である。ここで10TOPS→50TOPSという数字の根拠であるが、そもそもAIE-MLの性能というのはこちらを見る限りINT 8でTileあたり512Ops/Cycleとされる。

-

Photo11: 10TOPSというのはHawk PointではなくRyzen 7040ことPhoenix Pointの数字。Hawk PointはNPUの動作周波数を1.6倍にして性能の底上げを図った。

Phoenix PointのNPUが1GHzと仮定すると性能は512TOPS×20Tile×1GHz=10.24TOPSである。Hawk Pointだと動作周波数が1.6GHzで16.4TOPSほどになる計算だ。同じようにXDNA2を1.5GHzと仮定して計算すると24.6TOPSほどになるが、Sparsityを利用した場合は最大2倍の性能になるということで、ピーク性能はこの2倍の49.2TOPSほどになる。動作周波数がHawk Pointと同じ1.6GHzなら52.4TOPSほどになり、これはちょっと数字が大きすぎる。1.5GHzあたりを想定しておくのが無難だろう。とはいえこの試算が正しいとすれば、Sparsityが利用できない場合はHawk Pointの1.5倍程度のNPU性能にしかならない訳だが、これで十分かどうか?はCopilot+のModelというかNetwork次第である。今回AI PC向けと銘打って発売されており、その中でMicrosoftと共同でこの辺りを確認している以上、多分性能的に足りているのだろう、と判断するしかない(それだけCopilot+のModelは疎なもの、ということだろうか?)。

もう一つの特徴がBlock FP16である。これも先のレポートではMXFP8ではないか?と書いた。そのMXFP8であることは正しかったのだが、E5M2やE4M3ではなく、E8M0だったのが正解であった(Photo12)。OCP Microscaling Formats (MX) Specificationから当該箇所を抜き出したのがこちら(Photo13)であるが、要するに8つの値を一つの塊(k=8)としたうえで、個々のelementは符号+仮数部とし、共通のX(shared scale)に指数部を置いた形になる。こうなるとこの8つの値は共通の指数部を持つことになるので、あまり激しくデータがバラつくケースでは精度が落ちるが、似たような値であれば十分な精度になるという訳だ。BF16(符号+仮数部7bit+指数部8bit)と同じ精度を保ちながら、データ量をほぼ半減(厳密に言えば72bit÷128bit=0.5625なので、4割減といったところか)させることが可能になった、というものである。そして演算そのものは(指数部の部分を除くと)8bit演算で済むから、INT 8の場合と同様にピークで50TOPSが出る、としている(Photo14)。

ちなみに今後のロードマップとして、2026年までにXDNA 3が登場するとしている(Photo15)。ただしこれはClient-NextだけでなくVersal-Nextも含まれており、またVersalシリーズと歩調を取って投入されることになると思われる。