Intelの10nm FinFETプロセスに向けてARMのIPを提供

実際の取り組みについて、もう少し細かく紹介する。先のBall氏とAbbey氏のリリースをまとめると要点は次の2点である。

IntelとARMは共同で、Intelの10nm FinFETプロセスに向けて、ARMのPremier Mobile Processor CoreのIPを提供する

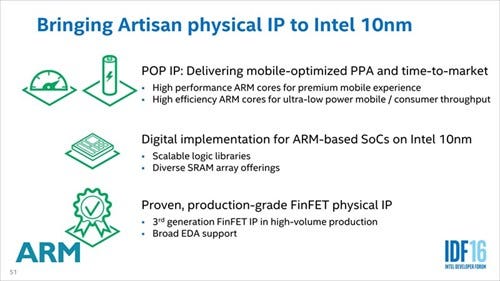

同じくIntelとARMは共同で、Intelの10nm FinFETプロセスに向けて、ARMのARM Artisan physical IPとPOP IPを提供する(Photo04)

|

Photo04:POP以外はIntelも自社向けには用意しているが、これはIntelが自社で使うことを前提にしたものだから、Foundryのユーザー向けになっていない。ユーザーが実績と定評があるIPを好むのは当然であり、Artisanのサポートは当然と言える |

まず1つ目について、以前こんな記事を掲載したが、ARMのProcessorを利用してSoCを作る場合は、そのメーカーは、ARMからLicenseを取得する必要がある。

これはSoCを製造するベンダー側の話だが、実はFoundry側にもLicenseが必要であり、これを取得していないFoundryはARMのIPを含んだSoCの製造ができない。実はIntelは、14nm世代ではこのFoundry Licenseを取得済みである。

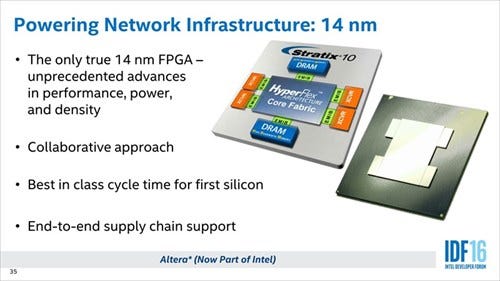

2013年にAlteraのStratix 10の製造に関するライセンスを結んでいるわけだが、このStratix 10の中にはQuad Cortex-A53を搭載するものがあるので、この時点でFoundry Licenseを取得済でないと非常に困ったことになるからだ。

このFoundry Licenseは、あくまで14nm世代に関する話なのだが、Alteraが10nm世代で引き続きIntelを利用することを明らかにしており、10nmでもFoundry Licenseを取得していたと思われる。ただ、AlteraがIntelの子会社となっているので、これを広い意味でのFoundry Licenseとみなすかどうかはちょっと微妙なところだ。何はともあれ、顧客の少ない14nm世代はともかく、広く顧客を集めたい10nm以降では真面目にFoundry Licenseを取得して製造できるようにすることは必須だったのだろう。

続いては2つ目の要点である。ARMはCPU/GPU IPのみならず、Artisanと呼ばれるPhysical IPを提供している。こちらはARMのCPU/GPU IPを使うときにはほぼ間違いなく利用されるIPであり、Ball氏のリリースの中でも"High Performance/High Density Logic Library・Memory Compiler・POP IP(for future ARM premium mobile cores)"を含むArtisan Physical IPが提供されるとしている。これを提供するのは誰か、というとIntel&ARMである。Physical IPだから、実際にはFoundryの提供するプロセス毎に異なった実装と最適化が行われることになる。

これはPOPも同じだ。元々ARMはCPU/GPU IPについてRTLベースで提供しており、実装はIPを取得したメーカー任せとなる。ところが最近の先端プロセスの場合、実装だけで半年、さらに最適化に1年とか膨大な時間とエンジニアコストが掛かる。

最近はEDAツールの性能が上がってきて、自動配線だけでも「そこそこ」使える物理実装が完成するが、あくまで「そこそこ」レベルで、そこからパラメータを変えながら延々と最適化を施したり、場所によっては手配線がまだ行われたりする(このあたりは、以前こちらでちょっと触れた)。

POPは、Physical IPほどではないにしても、ある程度プロセスに合わせる形でこの物理実装の最適化作業を行った「RTLよりももう一段深いレベル」でのIPを提供するものだ。これを利用することで顧客は自身での物理実装の時間を大幅に節約しつつ「そこそこ」よりはずっとマシな性能や消費電力特性を実現できる。

このPOP IPもまた、ARMとIntelが「これから」共同開発を行うことになる。"for future ARM premium mobile cores"という言い方は、Cortex-A73もしくはその先の世代のPOP IPを提供できるようにする、という意味合いと考えられる。

一点不明なのは、ARMがSystem IPとして提供しているCoreLink(SoC内のInterconnectやメモリコントローラ、システムコントローラ類)や、Mali GPU IPなどに関する言及がないことである。

GPUに関してはImaginationのPowerVRという代替案はあるが、InterconnectとかMemory Controllerなどをどうするのか、あるいは単に長くなるから省いただけで実際は提供されるのか、このあたりが現状ははっきりしない。これが提供されないようだと、Intelの10nmを利用してSmartphoneなどのSoCを製造するのはちょっと困難が伴うだろうと想像される。

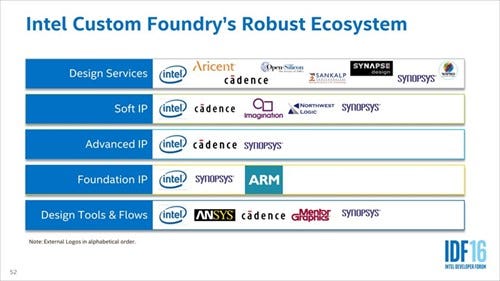

ちなみに開発環境としては、Cadence/Synopsys/Mentor Graphics/ANSYSといった大手がサポートを表明済であり、ASICを設計しようという昨今のユーザーにはきちんと対応できる体制が整えられているとする(Photo05)。

|

Photo05:古くからのユーザーだともう少し要望があるのだろうが、28nm以下のプロセスだともうこのあたりのメーカーが対応していれば問題ない、という見切りであろう。もっとも、では各社のToolが"どこまできちんと対応しているのか"はまだ分からない |

Intel 10nmプロセスの現状

ついでに、同時にIDFのTechnical Sessionで公開された10nm世代の現状についてもちょっと説明しておきたい。もっとも"現状"といっても実際のシリコンの状況などについて一切説明がなく、Intelの10nm世代と他社の10nm世代の比較といったレベルに留まっているのだが。

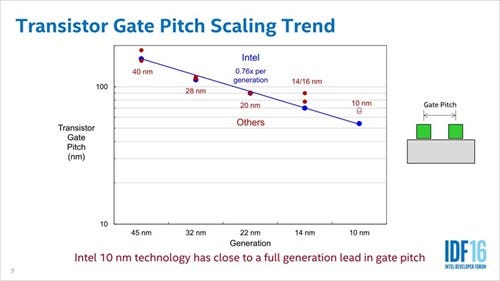

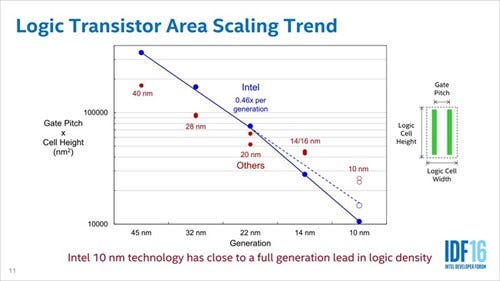

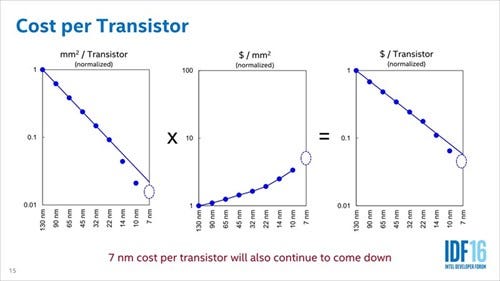

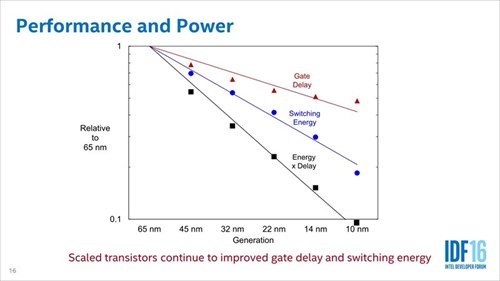

物理的な寸法を見ると、Gate Pitch(Photo06)はIntelが50nm台、競合は60~70nm台。Transistor Area(Phtoo07)も、競合に比べてずっと小さくなるとする。この結果として、トランジスタあたりのコストは順調に下げ続けているというのがIntelの主張だ(Photo08)。性能という観点でも、Gate Delayも減り、Switching Energyも減っているという(Photo09)。

|

Photo09:とはいえGate Delayに関しては、もうほとんど大きくは下がらない感じで、速度アップはあまり期待できない。ただし消費電力が引き続き順調に減っているので、性能/消費電力比の向上は期待できることになる |

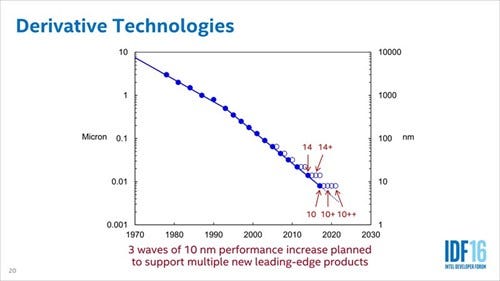

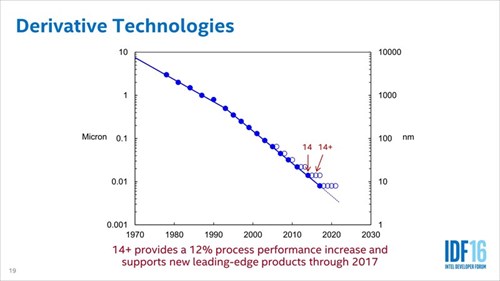

面白いのが次のスライドで、14nm世代については、2017年に14+という改良したプロセスをリリース(Photo10)し、2018年あたりまで使われると読める。さらに10nmでは10/10+/10++という3世代が投入され、2022年あたりまで利用されることになる模様だ(Photo11)。

|

Photo10:長らく出てこなかった(というか、放棄したと思われていた)High Performance Logic向けがリリースされる模様。ただし2017年の製品ということで、KabyLakeには間に合わないことになる |

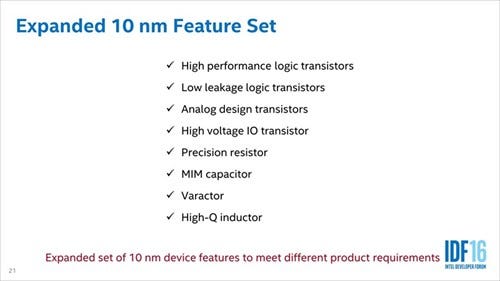

この10nm世代では、SoCあるいはAnalogに向けたコンポーネントも提供されることが明らかになった。これにより、Intelが言うところのIoT向け製品の開発も可能、というスタンスは崩していない(Photo12)。

|

Photo12:とはいえ、Embedded Flashはさすがに無理な模様。これをどうするかが、Intelの先端プロセスでIoT向けデバイスを作ろうとする場合に常にネックとなる部分で、これに関してもまだ答えは出ていない |

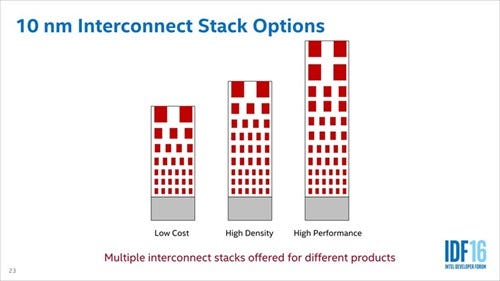

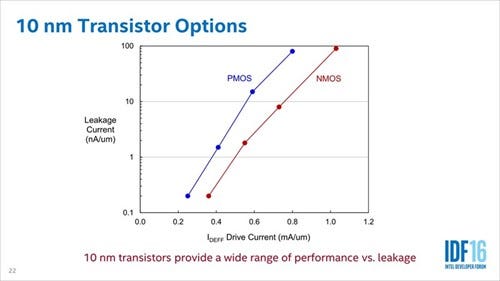

トランジスタの動作速度そのものはPhoto13のような感じで、よりLeakを減らす方向になっており、後はPerformanceとの兼ね合いで複数の動作特性を提供できるとする。また配線オプションとしては、低コスト~高性能まで複数の配線を提供できるという(Photo14)。

|

Photo13:VDDが明示されていないので比較が難しいのだが、2014年のIEDMにおけるIntelの14nm FinFETに関する論文の図と比較すると、同じ駆動電流だとよりリークが少ない傾向にある(例えばPMOSの場合、14nmではDrive Currentが0.2mA/μmの場合、概ねLeakは1nA/μmと報告されている) |

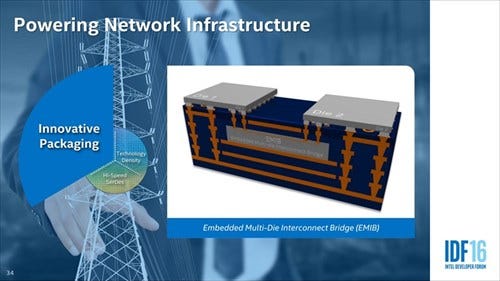

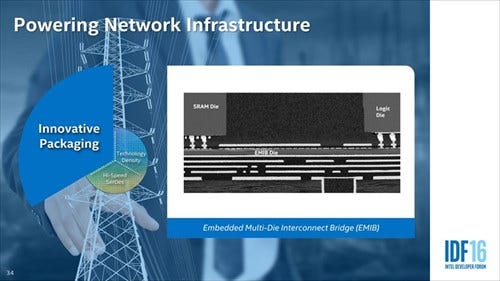

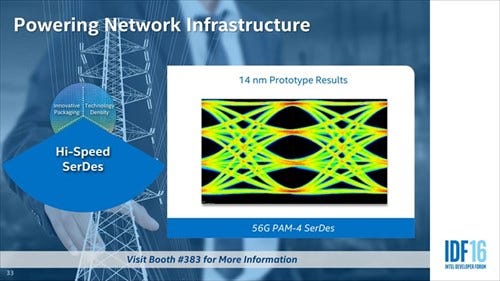

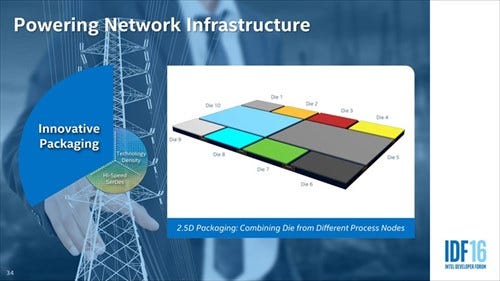

また、Foundryの話に戻るが、Intelはこの14/10nm世代をMobileのみならずNetwork機器向けSoCなどでも有用と見ているようで、56GのSerDes(Photo15)とかSilicon Interposer(Photo16)、EMIB(Photo17とPhoto18)などのオプションを提供できるとしている。

|

Photo15:基地局などではとにかく高速な転送が求められるが、さすがにBinaryで56Gは無理だったのか、PAM-4を使った28GHzの伝送のSerDesを提供する模様(PAM-4だと1Symbol=2bitなので、転送速度は56Gbps) |

|

Photo16:パッケージの上に、Siliconベースの中間層を用意して、ここでチップ同士を繋ぐ方式。パッケージに直接載せるよりも多数の配線を構築しやすい。TSMCはこれをCoWoS(Chip-On-Wafer-On-Substrate)として提供中だ |

その実例としてStratix 10ベースのDRAM SiP Deviceを示した(Photo19)。しかし、Network機器向けということになると、FPGAあるいはARM CPUではなく、それこそXeonなどのコアを組み合わせたSoCを、という要望も少なくないような気がするのだが、それに対してどう答えるのかは今回のセッションでは明らかにされなかった。

ということでかいつまんでARMとの提携、および10nm世代の現状をご紹介した。一言でまとめれば「10nm世代でも路線は変わらない」というあたりだろうか。問題は10nm世代が本当に2017年に製造開始できるのか、あるいは開始しても(14nmの時の様に)さっぱりモノが出てこないという事態に陥らないのか、というあたりである。こればっかりは、ふたをあけてみるまで分からないので、とりあえずは2017年まで待つしかなさそうだ。