Out-of-Order部(3)

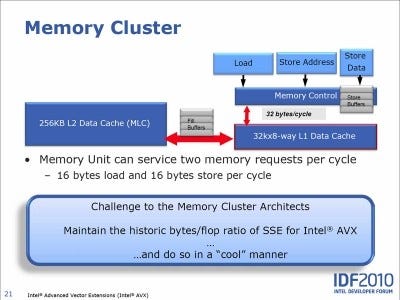

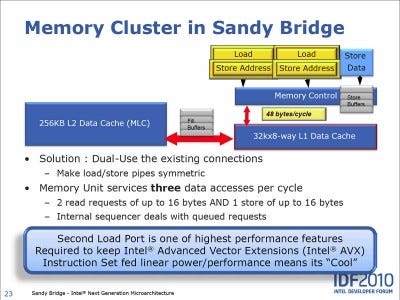

最後がPort 2/3/4にマップされるLoad Storeユニットである。従来のNehalemの場合、Load/Store Address/Store DataがそれぞれにMappingされており、SSEを使う分にはマッチした帯域であるが、AVXでは帯域が不足することになる(Photo14)。そこで、ポート2/3はどちらもLoad/Store Addressとすることで、同時に256bitのLoadとStore Addressが発行できるようになった。このあたりは概ね、以前説明したものがそのままであった。まぁプレゼンテーションでは専らSSEやAVXに着目しての説明であるが、勿論これは通常のx86命令でもその恩恵を受けられるわけで、このあたりもIPC底上げに貢献しているのではないかと思われる。