2015年11月に米サンタクララで開催されたARM TechCon 2015のレポートは既に3本ほどお届けした(その1、その2、その3)が、このレポートはちょっと毛色を変えて、そこで紹介された各ファウンダリのプロセス技術をまとめてみたいと思う。

12月に開催されたARM Tech Symposiaの場合、日本国内の半導体メーカーの減少に加え、新規にARMのIPを使って自社専用のASICを起こそうという顧客も少なくなったので、ARMの最新技術と、パートナー企業によるARMのIPを使って製造されたSoC(アプリケーションプロセッサとMCU)の製品紹介が主になる。

しかし、ARM TechConの場合、実際に自社でASICあるいはASSPを作ろうと計画しているメーカーのエンジニアがやってくる。これもあってか、Technical Sessionの中には少なからずプロセス絡みの話が入っている。

特に先端プロセスに関しては、ファウンダリによるものに加えて、EDAツールベンダーとメーカーが共同で発表を行うことも珍しくない。例えば今回でいうと、TSMCの10nm FinFETプロセスに対するCPUコアのImprementationは、ARMとCadenceの共同セッションであった。

ただ、ここでは普段の記事などで出てくる「xxプロセスなので消費電力が減るor動作周波数があがる」的な話はあまりない。何故ならその話をするには、あまりに多くのパラメータが絡んでくるからである。

とはいえ、ファウンダリ3社(TSMC、Samsung、GLOBALFOUNDRIES)の先端プロセスの話を聞ける有意義な機会であることに間違いなく、実際Intel以外の製品はこれら3社のどれかのプロセスで製造されているから、ここで出てきた話は自ずと未来のPC向け製品の話に繋がってくる。ということで、いくつか目に付いたトピックを紹介したい。

TSMC 10FF - メリットは大きいが設計がより困難に

「メモリ以外の」生産能力という意味では言うまでも無く世界最大のファウンダリとなっているのがTSMC(Photo01)。TSMC以外のデータは? ということではやや古いがこちらを参照してほしい。

|

|

Photo01:直接的な比較は出来ないが、TSMCのGIGAFABのページによれば、GIGAFABだけで2013年中に393万6000枚の300mmウェハを出荷したそうで、200mm換算にすると年間886万枚相当。月産74万枚である。これに200mm以下のFabを加えたほか、GIGIAFAB自体の製造能力も上がっている結果がこの数字ということだろう |

リンク先のFigure 2を見ると、300mmウエハのトップ4はどれもメモリベンダーで、ここからメモリを抜くと間違いなくTSMCがトップである。またメモリにはもう使われない200mmウエハでもTSMCがトップになっている。同社はGIGAFAB 12/14に加えて15も台湾に保有しており、今度は中国に16nmプロセスのFabを作るとか作らないとかいう話になっている(Photo02,03)。ここから考えると、今後も間違いなくトップリーダーの立場を維持していくだろう。

|

|

Photo02:2015年頭の状況と比較すると、GIGAFab 15のP5が新しく加わった |

さてTSMCのプロセスについて紹介すると、すでに16FFと16FF+は量産を開始している。これを利用した最終製品としてAppleのA9が広く出荷されているのはご存知の通りだ。16FFと16FF+は順調ということもあり、いまの関心は10nmに移りつつある。

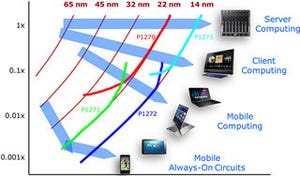

TSMCによると、10FFでは従来とおなじ動作周波数なら70%のリーク削減、同じリークならば動作周波数30%アップ(Photo04)としている。16FF+の場合、動作周波数を基準の1.4倍あたりまで引き上げたあたりでリークが急増、1.8倍あたりで垂直とは言わないまでも猛烈な跳ね上がり方をしているのが、10FFでは大分なだらかになっているのが分かる。

一方エリアサイズ(Photo05)も、大幅に削減可能だ。もともとTSMCの16FF/16FF+もSamsung/GLOBALFOUNDRIESの14LPE/14LPPも、トランジスタは16/14nmだが配線層は20nm相当なのに対し、10FFでは10nm相当のものになるから、理屈で言えば密度は4倍になる計算だ。

もっとも実際にはそこまで高密度化できない(特に配線層の制約が大きい)のだが、それでも大雑把に言って密度を倍にできるとしている。また先にLeakage、つまりStatic Powerの削減が成し遂げられるという話はあったが、Dynamic Powerもおおむね37%削減できるとしている(Photo06)。

とまぁここまでは良い事尽くめの話なのだが、ここから先は面倒な話が出てくる。10nmの設計は基本的にはevolution、つまり16nmの延長線上にある(Photo07)というのだが、IR drop(配線抵抗と電流の積、つまり消費電流)が非常にクリティカルになるという。

またDRC(Design Rule Check)のルール数も着実に積みあがっており、設計が壮絶に難しくなることが示されている。この設計のための指針がこちら(Photo08)なのだが、さらっととんでもないことが書いてある。これについては後で別の例が出てくるのでその折に触れるが、とりあえず設計はできても、そこから最適化に果てしない時間が掛かる(か、猛烈なコストが掛かる)という話である。

そのDesign Considerationはいくつか挙げられているのだが、先のPower Gridまわりで言えばPhoto09のような話がある。これは最適化しないPower Gridと最適化したものでは、同じ動作周波数でもエリアサイズが変わるというもので、Cortex-A9の場合に何も考えずに設計するとエリアサイズが1割ほど大きくなるという結果が出ている。もっと複雑な最近の回路では、もう少し差が大きくなるかもしれない。

配線層だが、10FFではPhoto10のような形になるそうである。最終的に配線層がどの程度になるかは設計次第だが、さらに層数が増える事は間違いない。余談ながら、10FFの場合M1~M3の構築にはDouble Patterningが必須となるそうだ。

|

|

Photo10:これはARMのArtisan PGAを使うことを念頭に置いた説明ではあるが、要するにStandard Cell LibraryはM1とM2を使う形。Artisan PGAはM3ではなく、Upper Gridの最下層を使う構成になるらしく、M2経由でM1までは長大なVIA(Power Grid Totem)を構成する形で繋ぐ模様だ |

10nm世代で必要とされる"Coloring"

さて、10FFでもう一つ、今度はARMとCadenceによるスライドを簡単に紹介する。P&R(Place and Routing)に関して、28nm世代からDouble Patterningが必須になったが、10nm世代ではもうDouble Patterningでは限界ということで、Triple Patterningが必須になった。この結果として、新たにColoringと呼ばれる概念が導入されることになった(Photo11)。

Coloringとは? という話は後述するとして、Photo12はDRCの数字だが、先のPhoto07と比べると20nm以降で急に増えているのがわかる。このあたりはEDAツールによっても変わるのだろうが、設計の際の制約条件がどんどん増え、最適解を見つけるまでの時間がより掛かる傾向にあるのは間違いない。

続いてColoringとは何か? の話。Multi-Patterningの場合、隣接する配線は別々のPatternにしないといけない(でないとパターンがくっついたり変形したりしてしまう)という問題がある。これを避けるために、配線というかパターンに仮想的な「色」をつけて区別するのがColoringという技法である。これを判りやすく示したのがPhoto13である。

|

|

Photo13:ちなみにこれはTriple Patterningの場合で、7nm世代で出てくるQuad Patterningでは当然色の数が4色になる。これは典型的な三色/四色問題(三色/四色定理)である。単に色分けだけならともかく、実際にはこれを踏まえた上での最適化が求められるから始末に負えない |

右上が悪い例で、このままだと緑のパターン同士が隣接しているので、このままリソグラフィを掛けると2つのパターンが分離不十分になる危険性がある。これを避けるためには、Color Orderを変えるとか、Cellの構造を反転させる、あるいは間を余分に空けるなどの配慮が必要である。

Photo13のような構図だけだと簡単と思われるかもしれないが、実際にはウン十億のトランジスタを集積した、ウン億近いゲートが集積される回路でこれを満たすのは(しばしば長い配線などもあることを考えると)非常に難しい。

この隣接した同じ色同士の配線の接触防止をOdd cycle prevent(奇閉路防止)と呼ぶが、これも設計時には配慮する必要がある(Photo14)。ちなみにここに出てくるGigaPlaceとかNanoRouteは、Cadenceの提供するEDAツールの名前だが、10nm世代ではこういうツールを使って配置配線を行わないとうまく行かない、という域に達している事を物語っている。

|

|

Photo14:NanoRouteの説明の左側は、3つの入力のうち2つと出力が三角形を成してしまい、ここでパターンが接触する例。Odd cycle preventでは右側の様に出力の場所を移動して、三角形が構成されないようにする |

先のPhoto12にも出てきたが、40nm世代あたりまでは手配線部分を残して最適化という話は良く聞いたし、28nm世代でも一部のメーカーは手配線で最適化といった話をしていた。ところが16nmとか10nm世代では、Photo12のグラフにも示すようにDRCの数が飛躍的に増えており、そろそろ人間の手作業で最適化とかがかなり難しい状況になりつつあることを示しているともいえる。