GDDR3ベースの512ビットバスとGDDR5ベースの256ビットバス

今度は、ROPユニットと綿密な関わりを持つメモリシステムについて着目してみよう。

GeForce GTX 200シリーズでは、各ROPユニットが64ビットメモリコントローラと接続されている。そして各64ビットメモリコントローラはx32のGDDR3 SDRAMチップ2つと接続されている。GeForce GTX 280はROPユニットが8基あるのでビデオメモリバスは合計512ビット(64ビット×8ROP)ということになる。

メモリコントローラとROPユニット群とはクロスバー接続になっており、512ビットのクロスバー型のメモリバスは、現行GPUとしては世界最大規模になる。なお、下位モデルのGeForce GTX 260はROPユニットが7基になるのでビデオメモリバスは448ビット(64ビット×7ROP)だ。

NVIDIAが今回もGDDR3を選択した大きな理由は、GDDR3がコストが比較的安く、そして安定供給が見込めるところにある。そして512ビットのメモリインターフェースの採用は、シェーダコアの規模拡大と高速動作に見合うメモリシステムを実現するためだ。512ビットのパラレルインターフェースといえばピンを出すだけで相当な物理スペースが必要なわけだが、それが実現できたのは、GeForce GTX 200シリーズが576mm^2(24mm×24mm)もの巨大なチップだからだ。

一方でRadeonは、Radeon HD 2900シリーズ(ダイサイズ400mm^2)からRadeon HD 3800シリーズ(ダイサイズ190mm^2)になったときにプロセスがシュリンクしてダイサイズが小さくなったことで、その物理スペース的制約から512ビットメモリインターフェースの実装が困難となり256ビットメモリインターフェースとなった。ちなみにRadeon HD 2900 XTは512ビットメモリインターフェースで、内部リングバスは内回り512ビット外回り512ビットであったが、Radeon HD 3800シリーズ時にはこれが256ビットメモリインターフェースとなり、内部リングバスも内回り256ビット、外回り256ビットに規模縮小されている。

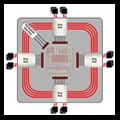

ダイサイズをコンパクトにまとめたRadeon HD 4800シリーズでは、その物理スペース的な制約からメモリインターフェースは256ビットとし、なおかつクロスバー接続タイプのメモリコントローラ(MC)を採用している。それまでリファインを重ねてきたリングバス方式のメモリインターフェースをATIは捨てたことになる。各MCは64ビットインターフェースでx32のメモリチップを2チップ接続するデザインとなっている。64ビットMCは4基搭載されており、全体としては64ビット×4=256ビットのビデオメモリインターフェースとなる。

前述したようにRadeon HD 4800シリーズではRadeon HD 2900/HD 3800シリーズのような共有型のL2キャッシュではなく、各MCの専属L2キャッシュの形で実装された。3DグラフィックスコアとMC+L2キャッシュとの接続は図中のHub(ハブ)を介したクロスバー接続となる。

前述したようにRadeon HD 4800シリーズはキャッシュシステムのリファインと内部バスの高速化の相乗効果で、内部は相当な高効率な動作を期待できるが、メモリシステムとしてのパフォーマンスにおける最終的なボトルネックはビデオメモリそのものの帯域に帰着する。同じ世代のメモリを使っていては、256ビット幅のビデオメモリインターフェースでは、512ビット幅には勝てるわけがない。

そこで、ATIが選択したのは、GDDR5 SGRAM(以下GDDR5)であった。

GDDR5を一言で説明するならば、ベースクロックの4倍のデータレートで動作できるビデオメモリということになる。Radeon HD 4870で採用されているGDDR5は900MHz駆動だが、データレートはその4倍の3.6GHz相当となる。

もちろん、ピーク帯域となる3.6GHzデータレートはバースト転送時に限られるが、大胆に解釈すれば、1.8GHzデータレートの512ビット・メモリインターフェースに近い性能が得られるということでもある。

これならば、GeForce GTX 280の512ビットバス接続の2.2GHz・GDDR3とも十分戦っていけそうではある。

ところで、GDDR5には、超高速クロック動作下におけるメモリアクセスにまつわるクロックのタイミングのズレ(Skew)を補正するための自己学習機能が持たされており、基板上の配線設計に余裕が生まれるというメリットがある。この自己学習型の歪み補正(de-Skew)の機能はRAMBUSのFlexPhaseテクノロジと酷似しており、超高速動作メモリにはこうした技術が欠かせないと言う状況になっている。

なお、GDDR5は将来的にはデータレート6GHz~7GHz以上(実駆動クロック1.5GHz~1.75GHz)のものが登場するとも言われている。ダイサイズをそこそこのサイズにしての256ビットメモリインターフェース採用という設計方針は時代に適合したソリューションであり、ATI限らず、近い将来NVIDIAも採用してくることだろう。