Hot Chips 28において、NVIDIAのJohn Danskin氏とDenis Foley氏が同社の最新世代GPU「Pascal」の発表を行った。

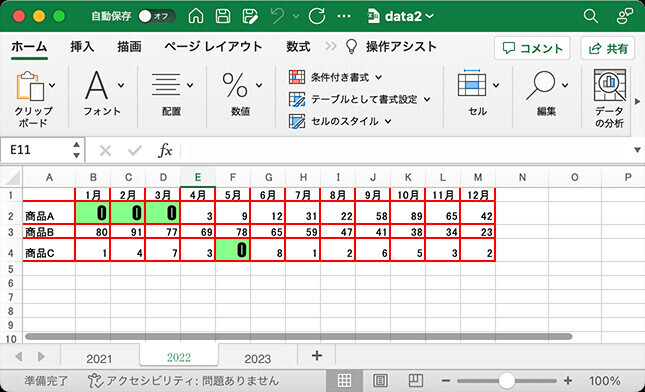

この発表は、筆者にとっては嬉しい発表であった。というのは、次の図の上側の図は2年前のHot Chips 26(HC26)でのNVIDIAの「Tegra K1」の発表の時の図である。この図は、一見、チップ写真のように見えるが、これはアーチストが描いた図で、チップ写真とは一致していない。例えば、Tegra K1は4個のCortex-A15コアと、1個の省電力コアを搭載して、big.LITTLE的な動作を行っており、それが図の下の方に書かれた4個の大きなコアと、中央に書かれた小さなコアで表現されている。しかし、実際には省電力コアはトランジスタの特性を変えたもので、ARMのbig.LITTLEのように小さいコアを使っているのではないので、本当のチップ写真ならば、5個とも大きさは同じはずである。

このような図を出すのは誤解を招くので、本当のチップ写真を公開すべきとNVIDIA主催の場では、何度も申し上げたのであるが、発表者は上の人に言ってくれということで、埒があかなかった。

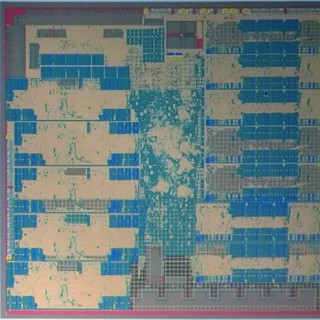

そこで、HC26での発表の後に、HC26の主催者に、学会の資料にこのような図を載せることは問題であると指摘した。このような指摘をしたのは私だけではないと思うし、これが効いたのかどうかも分からないが、今年のHot Chips 28の「P100」発表では、次の図の下側のように、本物のチップ写真が公開された。Danskin氏は、チップ写真に、枠で囲ってこの部分は何々という説明を付けることは認められなかったと言っていたが、説明は無くとも30個のSMが搭載されているのは容易に分かる。

GP100チップとHBM2の実装

Pascal GPUは、NVIDIAが2016年4月に発表した最新アーキテクチャのGPUであり、その中でも「GP100」は最上位の科学技術計算用のチップである。なお、GP100はチップの名前で、GP100を使うGPUボード製品は「Tesla P100」という名称になっている。

前述のような理由で、このチップ写真にはどこがSMとかいう説明は付いていないが、30個のSMが存在するのは容易に見て取れる。なお、2 SMは歩留まりを改善するための予備であり、製品としては最大28 SMとなっている。

そして、中央の部分に4MBのL2キャッシュが配置され、上辺と下辺にそれぞれ2個のHBM2コントローラとインタフェースが置かれていると思われる。とすると、左辺にはNVLinkとPCI Expressが置かれているのであろう。

GP100チップは、TSMCの16nm FinFETプロセスで作られ、610mm2という巨大なチップである。

なお、HBMは、JEDECという標準化団体の決めたHigh Bandwidth Memoryという3D実装を用いる広帯域DRAMの規格に準拠するメモリで、HBM2は、その第2世代の規格に準拠するメモリである。規格では最大256GB/sの帯域となっているが、NVIDIAのP100 GPUでは、180GB/sのものを使用している。

次の写真はSXM2モジュールの写真で、NVIDIAマークが付いているのがGP100チップで、その上下に各2個のHBM2 DRAMが付いている。HBM2はGP100チップに近接して置かれているので、写真では黒いHの字のように見えている。これらのチップは高密度で配線ができるシリコンインタポーザに搭載されており、GP100とHBM2は短い多数の配線で接続されている。そして、NVLinkとPCI Expressは下の写真に見られる2つのコネクタから接続される。

HBM2の採用とシリコンインタポーザの使用で、このSXM2モジュールは、PCI Expressカードに搭載されたK40 GPUと比較すると37%の面積になっている。また、この写真ではヒートシンクは付いていないが、ヒートシンクを付けても2U筐体に入る厚みに収まるとのことである。

なお、表面の写真の両側に並んでいる16個の黒いモジュールは、GP100チップとHBM2に電力を供給するDC-DCコンバータである。TDPは300Wであるので、各DC-DCコンバータは20W弱の電力を分担している計算になる。

次の図はGP100チップと4個のHBM2の部分の拡大写真であるが、前の図とは90度回転した向きになっている。HBM2はGP100チップにほぼ接するように置かれ、両者の間の信号配線は非常に短くなっており、寄生容量が減り、消費電力も抑えられている。

また、各HBM2は2チャネル構成になっているので、GP100チップから見ると8チャネルのメモリがあることになる。メモリは8チャネルであるが、L2キャッシュのスライスは32個と書かれているので、各チャネルに4個のL2キャッシュスライスが対応していることになる。そして、内部バスのバンド幅は3TB/sとなっているので、1スライスあたりのバンド幅は100GB/s程度で、64バイト幅ではないかと思われる。

次の図は、チップとシリコンインタポーザの部分の断面の写真と説明図である。HBM2は4枚のDRAMダイとその下のベースダイと呼ぶロジックチップをTSVで接続したものである。写真に見られるように、ベースダイはDRAMダイより少し張り出している。

シリコンインタポーザは高密度の配線ができ、GP100と4個のHBMの間には4096本の信号接続が存在する。そして、この部分のバンド幅は720GB/sとなっている。これは、同じ消費電力のGDDR5 DRAMを使うGPUの3倍のバンド幅である。

そして、一番上のDRAMダイはGP100チップと高さが揃うように、分厚いチップが使われている。そして、GP100とHBM2の部分は55mm×55mmと非常にコンパクトにできている。

シリコンインタポーザとチップの接続部分は非常に小さいので、従来のようにプローブを接触させてチップの検査を行うことができない。

HBM2の信号端子も触れないので、メモリメーカーは、ベースダイに検査用のパッドを設けて、そこにプローブを接触させてチップ上に作られた検査用の回路を動かして検査を行う。GPU側も同様に、検査回路を動かすための少数の検査用パッドを設けているのではないかと思われるが、検査方法については明らかにされていない。

一方、チップ間を接続するシリコンインタポーザは配線だけであるので、このような検査回路が作れない。このため、電気的な検査はできず、目視検査でショートや断線がないかを検査しているという。

また、シリコンインタポーザは、分厚い状態でGP100と4個のHBM2チップを搭載し、その後、インタポーザの裏面を研磨して薄くしているという。

4GBのHBM2は4枚のメモリダイの研磨による薄型化、TSVの形成などの手間がかかり、さらに、1枚のダイが不良でも全体が不良になるなど、歩留まりが低下する。また、シリコンインタポーザは、目視検査では、不良の見逃しがゼロにはならないし、チップ搭載後の研磨など手間がかかる。これらを合わせると、HBMの使用は、メモリバンド幅は稼げるが、かなりのコストアップになるという印象である。

Hot Chips 28 - NVIDIAのPascal GPUの実装とNVLink(後編)はコチラ