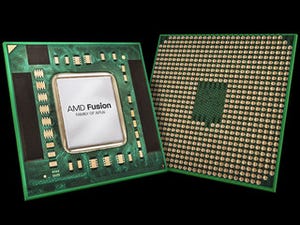

5月15日、これまでTrinityのコード名で知られていたAMDの第二世代APUが発表された。この第二世代APUは、PiledriverコアのCPUコアにVILW4世代のGPUを組み合わせたものであり、まず今回はMobile向けに投入される。この第二世代APUについて、事前に公開された情報などをまとめつつ、その構成を見てみたいと思う。

本稿のページ構成について、6ページ目から16ページ目までの各ページは、おもにRMMA 3.8を利用したアーキテクチャ分析を行っています。一般的なアプリケーションベンチマークについては、17ページ目から行っています。目的のベンチマークに直接アクセスしたい場合などは、こちらの目次ページの各見出しリンクの確認をおすすめします。

Trinityの構造

さて、Photo01が第一世代のAPUであるLlanoと第二世代のAPUであるTrinityの差を端的にまとめたものである。Llano、Trinity共にGLOBALFOUNDRIESの32nm SOIをつかって製造される関係で、ダイサイズ(228平方mm→246平方mm)、トランジスタ数(11.78億個→13.03億個)共に微増であるが、トランジスタ数は10.6%ほど増えてもダイサイズは7.9%の増加に留められており、その意味では実装効率を若干ながら改善した模様だ。

この効率の良さ、は性能面の特徴でもある。TrinityではMobile向けに45WのTDP枠を廃し、代わりに17WのTDPを追加している。概ね電力効率は倍増しており、IntelのIvy Bridgeとの奇妙な符合を見せている(Photo02)。

|

Photo02: 右のグラフの縦軸は"Performance/Watt"で、なので実際の性能はたとえばこれに35Wなり17Wなりを掛ける事で出てくる。その意味ではIvy Bridgeと同じく、性能レベルを変えずに消費電力を半減させたのがメインである。 |

内部構造は従来のLlanoと大きくは変わらず、CPUコアとGPUコア、Memory InterfaceとMedia Accelerator、Platform Interfaceが統合され、これがAシリーズチップセットに接続される形である(Photo03)。大きな違いとしては、まずアイドル時の消費電力は平均で1.08Wまで下げられており、CPUコアはK10由来のStarsコアから第二世代BulldozerであるPiledriverに入れ替わり、またGPUは一世代新しくなり、DisplayPortも追加された。またIOMMU V2も搭載されるなどしている(Photo04)。さて内部構造はPhoto05の通り。Stars 4coreからPile Driver 2Module/4coreになった関係で若干CPUコアは縮小しており、その分GPUコアの面積がやや増える形となっている。

|

Photo05: PCI Expressが24laneとあるが、うちx4 laneはチップセットとの接続に、x4 laneはDisplayPort出力用に割り当てられ、外部GPU用にx16 laneが残っている形。 |

さて、いよいよCPUコア。メインとなるPiledriverは基本的な構造そのものはBulldozerと大きくは変わっていない(Photo06)。主な改良点としては、オレンジで示されているようにFMA3やF16Cのサポート、IPCの若干の改善やリーク削減、CAC削減、動作周波数向上などが実現されている。もっとも基本がBulldozerコアだから、Starsコア並みにIPCが上がることはさすがに期待できないが。

そのIPに関わる改良点を示したのがPhoto07である。こうした多くの改良についてJoe Macri氏(Corporate Vice President and CTO of the Client Division)曰く「Starsコアはこれまでも随分改善を加えてきており、そうおいそれと手を入れられる部分は無い。ところがBulldozerは出来たばかりのコアだから、まだまだ手を入れられる部分が随分ある」と説明しており、こうした様々な改良でIPCを多少なりとも底上げできる、としている。

Memory Controller周りもまた随分手が入った(Photo08)。この世代での大きな特徴は、従来HTでのマルチプロセッサ/チップセット接続を考慮していた部分を完全に排除したことだろう。またメモリコントローラは1.5VのDDR3や1.35VのDDR3Lに加え、1.25VのDDR3Lにも対応している。これについてもMacri氏は「現状ではまだDIMMは存在していないが、将来の対応に備えた」としている。動作周波数自体もDDR3-1866までに対応している。また新たにAtomic/MAD(MCT Atomic Data Buffer)といった機能を追加している。これは要するにGPUとCPUの間で高速に同期を取るためのメカニズムであるが、面白いことにこれは独自の規格(Macri氏に「これはPCI Express Extentionと互換性のあるものなのか、それとも独自規格なのか?」と確認したところ「PCI Expressとの互換性は考慮していない」という返事があった」)であり、また対応できるのはTrinityに内蔵されるGPUと、GCN(Graphics Core Next)のGPU(つまりRadeon HD 7000番台)でのみ有効という話で、それ以前の製品では利用できないとのことだった。そのRadeon Memory Busの内部構造はこちら(Photo09)。GPUそのものの性能改善に対応してMemory Busも拡張する必要があり、ついに内部的には双方向256bitのバスに拡張されている。

次がTurbo Core 3.0である。Llanoの世代ではCPUのみがTurbo Coreの対象となったが、TrinityのTurbo Core 3.0ではCPUとGPUの両方がTurbo Coreの対象となる(Photo10)。このTurbo Coreによる性能の伸び代が大きく増えた、というのもTrinityの特徴で(Photo11)、製品にもよるが最大900MHzも動作周波数が上がることで、これまでよりも性能が改善されやすい、としている。

次がGPUコアである。Llano世代に搭載されていたものはVILW5世代のもので、たとえばハイエンドのA8-3870Kの場合では400sp構成だったが、TrinityではこれがVLIW4世代に切り替わった(Photo12,13)。「何でGCNを搭載しなかったの?」とMacri氏に確認したところ「(Trinityの)デザイン中はまだGCNが完成してなかったので間に合わなかった」という単純な答えが返ってきた。もっともVILW4をそのまま持ってきたわけではなく若干の改善も施されているようだ(Photo14)。

次がUnified Video Decoderであるが、Trinityではこれが第三世代となっており、新しいフォーマットのサポートや、出力ストリームの強化などが行われた(Photo15)。エンコードに関しても同様で、ついにCPUからはRate Controlだけを行えば、あとは完全にハードウェアでのエンコードが可能となっている。

|

|

Photo15: これまでは不可能だったHD Stream 2本の同時再生が可能になったのが大きなポイント。またMPEG-4のサポートも地味に便利である。 |

Photo16: このあたりの特徴はIvy Bridgeに搭載されるIntel QSVと同じく。もっともこれを利用するためにはアプリケーションが対応していないといけないというのも、これまた同様。 |

画面出力関係では、3ch/4画面の出力が目新しい(Photo17)。これにあわせて、7.1ch Audioを最大で同時4chまで出力できるようにされている(Photo18)。また搭載するHD Media Acceleratorでは再生画像の画質向上の機能を搭載する(Photo19)ほか、新たにAMD Quick Streamと呼ばれるソフトウェアが搭載された(Photo20)。このAMD Quick StreamはTrinityでのみ利用可能で、Llanoなどでは利用できないとのことだった。