既報の通り、英ARM HoldingsはCOMPUTEX/TAIPEI開催前日である6月3日に、Cortex-A12をはじめとする新製品の発表会を台湾で開催した。この発表会の内容、及びその後もう少し詳細について個別インタビューの機会があったので、まずは技術的な範囲に絞ってレポートしたい。

発表製品一覧

発表会はIan Drew氏(Photo01)が(なぜか)自転車で登場後(Photo02)、まずはマーケティング的なポジションを説明したあとで製品の詳細に移った。今回発表されたのは、CPUコアとしてCortex-A12、GPUとしてMali-T622、Video ProcessorとしてMali-V500、そしてこれらのPOP IPという大きく4つとなる(Photo03)。まずCPUコアであるCortex-A12だが、これは現在のCortex-A9の後継という扱いであり、Cortex-A15とCortex-A7の間に入る製品となる。同じ動作周波数であれば最大で40%高速とされており、最大4コアの構成である。最初の製造ファウンダリはGLOBALFOUNDRIESであり、SoCベンダーのひとつはVIA Technologiesであることが明らかにされている(Photo04)。

|

|

|

Photo01: Ian Drew氏(Chief Marketing Officer & Exective Vice President, Business Development)。氏は6月5日にCOMPUTEXの基調講演も行うことになっている。 |

Photo02: 自転車の意図はさっぱり不明。 |

次がMali-T622であるが、こちらは既存のMali-T600シリーズのエントリモデルという扱いであり、特徴としては従来のT600シリーズと比較して最大50%もの性能/消費電力比の改善を実現したとしている(Photo05)。また、Mali-V500 Video Processor(Photo06)は最大8つのVideo Coreを持ち、1つでFull HDの60fpsでのEncode/Decodeが、最大で8コア構成が可能でこの場合は4K解像度で120fpsのEncode/Decodeがそれぞれ可能である。

最後がこれらのPOP(Processor Optimization Package)である。Photo03にもあるとおり、Launch PartnerはGLOBALFOUNDRIESであり、こちらの28nm SLP(Super Low Power)に向けたPOPが提供される。またTSMCの28nm HPM(High Performance Mobile)に対応したCortex-A12とMali-T622のPOPも提供が開始される。これらは発表が行われた6月3日の時点でSoft IPとあわせてAvailableという話であった。

Cortex-A12

発表会とは別に、もう少しCortex-A12の中身をJames Bruce氏(Photo08)に伺う機会があったので、以下ご紹介したい。まずは内部構造から。

Cortex-A12は2-issueのSuperScalar/Out-of-Orderのパイプライン構造を持つコアであり、この点ではCortex-A9に良く似ている。またパイプライン段数は11段で、これもCortex-A9に同じである。ただしこれらは既存のCortex-A9の改良とかCortex-A7/A15の改造というわけではなく、「Microarchitectureに関してはゼロからフルスクラッチで開発した」(Bruce氏)との事。開発開始時期は2006年だそうで、7年ほど掛けたことになる。ここまで時間が掛かった理由は「並行して他にもCortex-A7/15やCortex-A50シリーズ、Cortex-M/Rといった製品も開発しなければいけなかったので、エンジニアリングリソースがいくらあっても足りない」という現実的な理由だったそうだ。

具体的にどんな点をEnhanceしたのか、について詳細はまだ未公開(何れ公開するが現時点ではまだ公表できないという話であった。ちなみに日本でも発表会を開催する予定で、7月~9月のどこかとの事。その頃にはもう少し詳細が公開されるという事だった)であり、例えばDecodeは2-issueになるが、Dispatchがどうなるかなどについてはまだ説明できないとの事だった。ただCortex-A9の場合、Load/Store Unitが1つのDispatch Portを共用しているのがボトルネックになっているという話は広く知られており、これに関してのEnhancementがあることは伺わせていた。

ちなみに11段というパイプラインはあくまでもALUのもので、Load/StoreとかBranch Missがあった場合の段数などは細かく見ると一緒かどうかはまだ公表できないとの事であった。

ではどうやって40%ものPerformance Gainを得たかについて氏は詳細は語らなかったものの、「例えばCortex-A5とCortex-A7は同じSingle-IssueのIn-Order Pipelineだが、性能は20%改善している。それと同じように様々なOptimizationを行ったことでこの性能改善を実現した」と説明した。

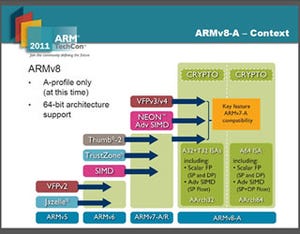

Cortex-A12とCortex-A9を外から見た場合、最大の違いはCortex-A7/15で導入されたLPAE(Large Physical Address Extention)と、Virtualization/TrustZoneの導入である。Cortex-A15は40bit、Cortex-A7は36bitの物理アドレスをサポートしており、OSが対応していればアプリケーション(というか、Thread)単体でのメモリ空間は4GBに制限されるもの、全体としては最大1TB(Cortex-A15)のメモリを利用できる。Cortex-A12もCortex-A15同様に、最大1TBの物理アドレスをサポートするそうだ。逆にアプリケーションから見ると、Cortex-A12はCortex-A9と極めて似ており、「Cortex-A12の最適化方法はCortex-A9と同じであり、Cortex-A9向けに最適化されたアプリケーションはそのままCortex-A12での動作に最適である」(Bruce氏)としている。

細かいところでは、Cortex-A9の場合FPUあるいはNEONはOption扱いであるが、Cortex-A12では標準でこれらが搭載されるそうである。これは発表時期の違いと使い方の違いがあり、Cortex-A9の発表当時はFPUを使うようなアプリケーションがMobile向けには存在しなかったし、いまではCortex-A9はEmbedded向けに広く使われており、こうした用途ではFPUやSIMDは必要ないことも多い。ところが現在は、例えばJavaでDouble Precisionを簡単に利用できるし、ゲームなどでFPUを使う事も多い。またCortex-A12はCortex-A9と違い、Mobile以外の用途に使うことを考えていないそうで、その意味ではCortex-A12はCortex-A9の後継といいつつも、必ずしも完全にCortex-A9を置き換える訳ではないそうだ。

またCortex-A12は、Cortex-A7と組み合わせてbig.LITTLEを構成することは可能ではあるが、そうしたニーズがあるかどうかは顧客次第という話であった。

最後にプロセス周り。このあたりは最終的にファウンダリ次第という部分もあってBruce氏の口もやや重かったのだが、TSMCでは28nm HPM、GLOBALFOUNDRIESでは28nm SLPを選んだ理由について「High PerformanceとかLow Powerといった用語の意味は、ファウンダリによって違っているので、別々のファウンダリのプロセスの名前は直接比較できない」との返事。「ではARMから見ればTSMCの28nm HPMとGLOBALFOUNDRIESの28nm SLPは同じものか?」と確認したところ「いやそういう訳ではないのだが」と歯切れの悪い返事が。要するにGLOBALFOUNDRIESは今のところ28nmはSLPしか実用化できておらず、あるいみ苦肉の策だったのだろう。