既報の通り、Intelは5月4日(日本時間の5月5日午前1:30)にTechnology Briefingを開催し、ここで22nmのTri-Gate Transistorに関する説明を行った。このTechnology BriefingそのものはWebCastの形で配信されており、利用されたプレゼンテーションなどと併せてこちらからアクセス可能になっている。

この22nm Tri-Gate Transistorに関する技術的な考察は既にAndo先生のレポートが挙がっているのでお任せすることにする。ちなみに2002年9月にIntelが初めてTri-Gate Transistorを発表した時の内容は、高梨名義でこちらにレポートさせていただいているので、併せてお読みいただければと思う。

さて発表そのものは筆者もWebCastで視聴しただけで、質問などをする機会には恵まれなかったのだが、5月6日にインテル(株)のご好意により電話会議の形で改めて説明を受けると共に、Q&Aを行う機会に恵まれたので、これも併せて(Ando先生のレポートに無い部分を)少し補足しておきたい。

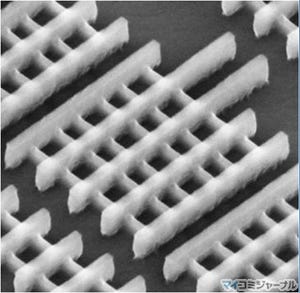

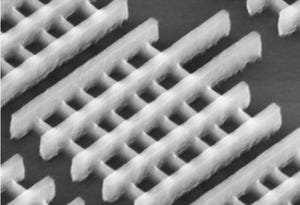

先にも触れたとおり、Intelは2002年に最初にTri-Gate Transistorの試作を発表する。この当時はまだ60nmでの製造だったから、今に比べれば大幅に大きいとも言えるが、当時量産に利用していたのははまだP860/P1260(8inch及び12inchウェハによる0.13μmプロセス)だったから。これに比べればだいぶ先端プロセスだったことになる。Intelはこれに引き続き開発を進め、2007年の段階で22nmプロセスでTri-Gate Transistorを使うことを決定したとする(Photo01)。2009年9月に開催されたIDF Fall 2009の基調講演でIntelは22nmプロセスを使ったSRAMテストチップのウェハを公開したが、実はこれもTri-Gate Transistorを使って製造されたものだったことが今回明らかにされた(Photo02)。実際当時の資料を見ても、Tri-Gateを伺わせるものは皆無で、逆になぜ今になってこれを公開したのか? というのはやや謎である。

|

Photo01: 例えば2006年のTri-Gate SRAMに関する話はこちら |

|

Photo02: 当時のプレスリリースはこちら。Tri-Gateという言葉はどこにもない。 |

ところでこの22nm Tri-Gateを使う最初の製品がIvy BridgeベースのXeonやCore iシリーズ(Photo03)、これに続きAtomベースの製品にも適用を考えているという話は既にレポートされている通りだが、ここで抜けている製品がある。ということでQ&AでAndy Tryba氏(Director of Corporate Strategy-Business Clients)に「Itaniumは22nmに移行しないのか?」とたずねた所、「現時点では具体的にItaniumを22nmに移行するための計画はまだ公開していない」としつつ、「Intelは引き続きItaniumのアーキテクチャに投資を行ってゆく予定で、それにはSiliconやProcessも含まれる。今の時点では具体的な話は出来ないが、今後の展開を期待してくれ」という、まぁ型どおりの答えが帰ってきた。Itaniumの場合、こういう芳しからぬニュースもあり、決して将来が楽観できる状況ではない。こちらの記事にあったIDFにおける説明というのはたとえばこちら(Photo04)であるが、Ivy Bridge世代がもう22nm間近なのに対し、32nmのPoulsonすらまだ出荷開始されておらず、そのためかKittsonに至っては未だにProcessがTBD(To Be Defined)扱いされている状態だ。Itaniumの場合、開発に時間が掛かっている関係で必ずしも全プロセス世代をカバーしているわけではなく、なのでいきなり22nmを飛ばして14nmプロセス、という可能性があるあたりかTBDの主な理由という気がする。そもそも今はPoulsonの出荷を何とかするのが第一義で、Kittsonの事はその後考えるというモードなのかもしれないが、何にせよItaniumの事は22nm世代は当面考えないでよさそうである。

|

Photo04: これはIDF Beijing 2011における"Standardizing Mission Critical Data Center Infrastructure"というセッションのもの。 |

さて、話を戻す。まず今回発表されたTri-Gate Transistorと、Intelが2002年に発表したTri-Gate Transistorでは何が異なるのか? を今度は22nmプロセスのProgram ManagerであるKaizad Mistry氏(Vice President, Technology and Manufacturing Group, Director, Logic Technology Integration)にうかがった所「22nmのTri-GateはIntelがこれまでに発表してきた歪シリコンとかGate-Last方式のHigh-K Metal Gateとコンパチブルな構造である」という答えだった。最初に発表したTri-Gateは単にTri-Gateなだけで、歪シリコンやHigh-K Metal Gateは採用していない構造であり、今回のものはこれまでのIntelの量産プロセスの延長にある構造だ、という話であった。

ついでに「昨年までのロードマップでは193nm ArF液浸+マルチパターニングで露光を行うという話だったが、Tri-Gateもこれで行うのか?」と確認したところ、その通りだという話であった。ただ、マスクの枚数は? と聞いたところそれは公開できない、という話であった。Mistry氏は「ただ、トータルのコストは2~3%増しでしかない」と強調しており、ここから察せという話である。

もっとも、このコストの話は非常に微妙である。2~3%増しのスライドはこちら(Photo05)であるが、「何と比べて」2~3%増しなのかという主語を明確にしていない。これは要するにプレナー型のBulkタイプと比較して、という話と考えられる。で、マスクの枚数は実のところ3Dにしたから劇的に増えるというものではない。そもそも今のトランジスタの場合、単純に1回の露光→エッチングだけで回路が作りきれず、複数回の露光→エッチング→CMPを繰り返して行う必要がある。これは歪シリコンとかHKMGなど新技術を導入するたびに少しずつ回数が増えており、今では結構な回数が必要になっている。これはIntelのものではないが、IEDM2009でIMECが22nmでFinFETを使ったSRAMを試作した報告をしており、この際には合計4回の露光が行われている。おそらくIntelのTri-Gateもこの程度の露光→エッチング→CMPの回数を行っており、プレナー型に比べて1回増えていると考えられるが、この増加分のコストが全体から見て2~3%である、というのがMistry氏の答えである。

問題は、Tri-Gateでなく従来のプレナー型を使ったとしても、22nmプロセスが(32nm同様に)ダブルパターニングで済むのか疑わしいところだ。IMECの論文ではダブルパターニングで済んでいる様だが、こちらはあくまで研究段階のレベルの話なので、量産工程にそのまま適用できるかちょっと疑わしい。大体ダブルパターニングであれば別に隠す必要も無いと思われるから、おそらく22nm世代では最低でもトリプルパターニングが必要になっているのではないかと思われる。当然マスクコストはパターニングに比例するからダブル→トリプルで50%増しになる計算だが、これは別に3D構造でなくても同じだということで、勘定に入れていない気がする。というよりも原価に占めるマスクコストの割合がどの程度か、というのはそのマスクでどれだけの数の製品を製造するかで大きく変わってくる訳で、敢えてこのあたりをぼやかす回答だった、と考えられる。

以下余談であるが、ついでにこちらで取り上げた、P1272の話を「Intelは2010年までP1272が15nmないし16nmと言っていたのに、なぜ今は14nmとなったのか?」とMistry氏に伺ってみた(Photo06)。すると「それは大変良い質問だが、今はまだ22nmより先のプロセスの話をすることはできない」とした上で「15nmないし16nmが14nmになったのは名前だけの話ではなく、本当に変わった(Real Change)ということだけは言える。スケーリング則から言えば、22nmから14nmというのはおかしいのだが、ただ次は14nmになるということは間違いない」という、非常に含みの多い返事が返ってきた。

|

Photo06: こちらと比較していただくとわかり易い。 |

更に「Photo06で、2015年には10nmがP1274というProcess Nameになっているが、これは10nmも300mmウェハで製造されるという理解で良いのか?」とたずねた所、「今私はそれに関して議論することは出来ないのだが、300mmウェハバージョンの10nmプロセスがP1274である。これ以上の事は今はいえない」という、これも非常に含みの多い返事であった。

ここから考えると、やはり筆者が先のレポートで推定した「Intelは2015年の10nmプロセス世代から450mmウェハを導入し(とは言え全量450mmは無理があるので、おそらく300mmと450mmの混在になるのだろう)、これに先立ち14nm世代でEUVを導入する予定」というプランにはそれなりの現実味がありそうだ。ちなみにP1274の世代も、以前は11nmと言っており、EUVの導入に伴いこちらも若干シュリンクして10nmになったのではないか、と思われる。少なくとも今回のQ&Aでは、この筆者の推定を覆すような返事が一切返ってこなかった、というのはなかなか興味深いものであり、当分このあたりを注視する必要がありそうだ。