VLSIシンポジウム 2024におけるプロセス・デバイス技術分野(従来のVLSI Technology Symposium)の採択論文数は95件。そのうち、今回はデバイス・プロセス部門の注目論文の最後として高密度2.5D実装および3Dトランジスタ垂直積層に向けた3件の取り組みを紹介する。

Foveros Face-to-Faceアーキテクチャによるシリコンインターポーザと高密度MIMキャパシタ集積をIntelが発表

- Integration of Si-Interposer and High Density MIM Capacitor on 2.5D Foveros Face-to-Face Architecture(論文番号:T9-1)

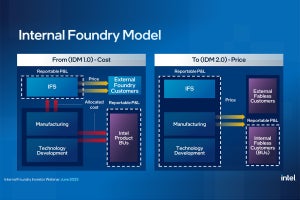

シリコンインターポーザを介して異なるコンピューティング要素を集積することで、ムーアの法則を超えたスケーリングの実現が期待されている。Intelは、パッシブシリコンインターポーザにより異なるチップレットを、バンプシリコン貫通電極を通じて、36μm間隔の微細マイクロバンプでデバイス面同士の貼り合わせ接続が可能であることを報告する。

このシリコンインターポーザには、電圧低下や雑音を抑制するための高密度MIMデカップリングキャパシタが集積されており、実際の製品においては、シリコンインターポーザ中あるいはチップレットに埋め込んだ高密度MIMキャパシタを用いることができるとしており、発表内容としては高密度MIMキャパシタの製造工程や電気特性、信頼性評価、高密度MIMキャパシタを集積したシリコンインターポーザによる性能向上などが予定されている模様である。

-

(左)シリコンインターポーザバンプおよびパッケージを介したトップダイへのインターポーザ接続を示す断面図、(右)DDRのシステムレベルインピーダンスプロファイルへの高密度MIMキャパシタンスへの影響 (出所:VLSIシンポジウム委員会。以下すべて同様)

熱影響を考慮したオングストローム世代のブロックレベルPPA性能評価をimecが発表

- Thermal Considerations for Block-Level PPA Assessment in Angstrom Era: A Comparison Study of Nanosheet FETs (A10) & Complementary FETs (A5)(論文番号:T5-4)

imecは熱影響を考慮したブロックレベルPPA(性能・消費電力・面積)性能のNSFET(ナノシートFET)とCFET(コンプリメンタリFET)の比較結果を発表する。

NSFETとCFETはそれぞれA10、A5世代というオングストローム世代の技術として期待されている。オープンソースの多数コアアーキテクチャを用いた解析の結果、A10からA5世代で2.5%のFmax増加、25%の電力低下、27%のサイクル当たりの電力低下、35%の面積縮小が見積もられ、結果として0.7V/25℃の環境では15%の電力密度増加となるという。このPPA性能評価手法は動的な熱影響の管理が必要なアプリケーションにとって重要となるパッケージレベルの高速熱解析が可能なシミュレータを備えており、温度に対して指数関数的に発生するリーク電力増加を考慮したものとなっているとする。

また、今回の解析から、A10世代を0.7Vで動作させるときと同じTj,maxを維持するためには、A5世代において64mVの動作電圧低下と10%の周波数低下が必要だが、その場合においてもシステムのスループットはA5世代で40%の改善があることが分かったという。

縦型ロジック・メモリ応用に向けた、極薄In2O3チャネルと厚膜In2O3ゲート電極で構成される高信頼性な全酸化物材料トランジスタをPurdue大学などが発表

- Highly Robust All-Oxide Transistors with Ultrathin In2O3 as Channel and Thick In2O3 as Metal Gate Towards Vertical Logic and Memory(論文番号:T4-1)

米パデュー大学とSamsung Electronicsの共同研究チームが、三次元垂直集積化に向けて、原子層堆積法(ALD法)により成膜したIn2O3膜をチャネルだけでなくゲート電極、ソース・ドレイン電極すべてに適用した全酸化物材料トランジスタの実証を報告する。

試作した平面型の全酸化物材料トランジスタは106以上の電流オンオフ比と低ばらつき、そして正と負のバイアスストレスに対するしきい値シフトがそれぞれ5mV、50mVという高い信頼性を示したという。また、試作した垂直チャネル型の全酸化物材料トランジスタでも、105以上の電流オンオフ比、160μA/μm以上の高いオン電流を示したとするほか、垂直チャネル型の全酸化物材料による強誘電体トランジスタ(FeFET)も試作からは、1.85Vのメモリウィンドウと1012回の書き換え耐性、そして10年以上の保持時間を示すことを確認したとしており、この成果により将来の高集積回路に向けて、ALDによる酸化物半導体を基盤とする、垂直チャネル型の全酸化物デバイスの有望性が示されたこととなる。

-

(左)10nm厚のIn2O3ゲート電極を有するALD法による垂直型の全酸化物トランジスタの高解像度断面TEM像およびEDSマッピング像、(右)ALD法による垂直型In2O3 FeFETの室温でのメモリ書き換え耐性と保持時間特性

なお、このほかプロセス・デバイス技術分野では以下の2つのテクノロジーフォーカスセッション(TFS)が予定されており、招待論文と一般論文で構成されている。

- TFS1 | Oxide Semiconductor's applications in BEOL

- TFS2 | Backside of Silicon : from power From Power Delivery to Signaling

TFS1では、招待講演としてGeorgia TechのDatta,Suman氏が「Amorphous Oxide Semiconductors for Monolithic 3D Integrated Circuits」、TSMCのWang, Chun-Chen氏が「P-type SnO Semiconductor Transistor and Applicatio」と題した2本が講演が予定されているほか、TFS2でも、同様にSamsung ElectronicsのKim, Byung-Sung氏が「Expanding Design Technology Co-Optimization Potentials with Back-Side Interconnect Innovation 」、Georgia Institute of TechnologyのVanna-iampikul, Pruek氏が「A Design Methodology for Back-side Power and Clock Routing Co-Optimization」という題でそれぞれ講演を行う予定となっている。