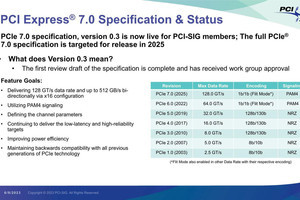

PCI-SIGは米国時間の4月2日、「PCI-Express 7.0」の「Revision 0.5 Draft」が完成し、これをメンバーレビューに回した事をアナウンスした。

PCI Express 7.0は以前[ご紹介したように](https://news.mynavi.jp/techplus/article/20220623-2376490/2、以下のような構成が想定されている。

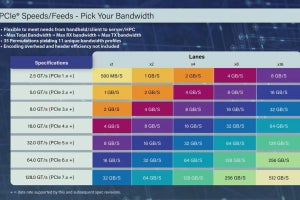

- 信号速度は64GBaud

- 変調方式はPAM4

- エラー訂正はLight FEC+FLIT

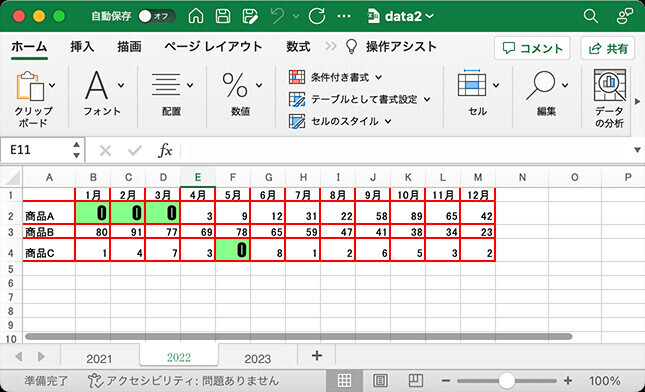

これによりx16なら512GB/sec、x4でも128GB/secの帯域を利用可能となっている。もっとも当初のPCI Expressの牽引役であったGPU(≠GPGPU)はすでにTargetから落ちており、800G Ethernet、AI/ML、Hyperscale Data Centers、HPC、Quantum Computing、Cloudなどがターゲットとなっている。

一番最初に立ち上がるのは恐らく800G/1.6T EthernetのI/Fで、これと並行してAI/ML向けアクセラレータの接続(アクセラレータ同時の接続は独自だったり、それこそUltra Ethernetの様なものが担うが、アクセラレータとホストCPUの接続にはPCI Expressが利用される)であるが、後追いの形でCXL Memory/StorageやSwitchなどにも利用されることになると思われる。2023年6月にRevision 0.3がリリースされており、ここからほぼ9か月といったところである。

現在はまだRevision 0.5であるが、この時点で技術的な骨子はほぼ固まり、ここからはメンバー企業が本当にこの仕様でハードウェアを製造して問題無いかの検証を行うフェーズに入る事になる。なので一般には大きな仕様の変更は発生しないはずであるが、Revision 0.7で仕様が固まり切らず、0.71をリリースする羽目になったVersion 3.0の例もあるため、今後は仕様変更が無いとは断言しかねる。

2024年6月12日に予定されている「PCI-SIG Developers Conference 2024」でRevision 0.7までDraftが上がるのかはちょっと微妙なところで、時期的に言えば7月か8月位にRevision 0.7 Draftがリリース、年内にDraft 0.9までいければラッキーで、1.0のSpecificationのリリースは2025年になると思われる。もっとも当初から2025年のリリースを予定していた事を考えると、今のところはオンスケジュールと考えて良いだろう。