東京理科大学(理科大)は3月17日、「スピン軌道トルクメモリ」(SOT-RAM)の読み出し信頼性を向上させるため、新たな読み出し経路を持つ「両方向読み出し方式」を提案し、これにより磁化反転電流としては従来経路より10倍程度のディスターブ低減が可能になったことを発表した。

同成果は、理科大 工学部電気工学科の河原尊之教授らの研究チームによるもの。詳細は、IEEEが刊行する磁性とその材料やデバイスなどに関連する物理学と工学全般を扱う学術誌「IEEE Transactions on Magnetics」にオンライン掲載された。

超低消費電力型デバイスの実現手法の1つとして、次世代磁気抵抗RAM(MRAM)の開発が進んでいる。現在、STT-RAMの製品化が進んでいるが、さらなる書き込み電流低減と高信頼化が必要とされている。そうした中で次世代MRAMとして期待されているのが、スピン軌道相互作用を用いて書き込み電流を1桁低減できるSOT-RAMだという。

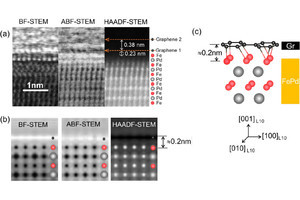

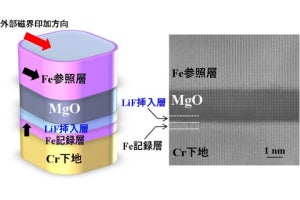

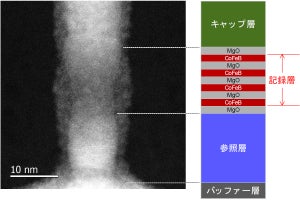

SOT-RAMでは、磁気トンネル接合に接続された重金属層に書き込み電流が流れ込み、スピンホール効果により、書き込み電流が純粋なスピン流を生成し、そのスピン流が自由層に送られて書き込み操作が行われるため、SOT-RAMでは読み出しと書き込みの電流経路が異なり、それによりSOT-RAMではディスターブは小さいと考えられていた。

これまで、STT-RAMとSOT-RAMの読み出し機構は同一であることから、読み出し障害も同じであると考えられていたが、河原教授らは、SOT-RAMが読み出し時に障害を起こす原因はそれだけではなく、スピンホール効果によって誘導されたスピン流に起因する障害も起こりうることをSOT-RAMのメモリセルに記憶された値を読み取る際に比較的大きな電流が自由層に流れ、それによって記憶された値が意図せずに逆転し、読み出し障害が起こるという課題から発見。今回の研究では、新たに発見されたこの固有の問題の解決案として、読み出し操作中に、読み出し電流を重金属層内で両方向に流す、両方向読み出し方式が提案された。同方式であれば、スピンホール効果により生成されたスピン流が相殺されることから、SOT-RAM読み出し障害を起こす原因が取り除かれて安定し、信頼性の高い読み出しが可能となるという。

提案された両方向読み出し方式SOT-RAMの実現に向け、材料パラメータ依存性、素子サイズ依存性、およびメモリセルアレイ抵抗依存性の検討が実施され、異なる磁化容易軸を持つ材料で生じる障害の調査から、提案方式を用いればいずれの材料でも不必要なスピン流が解消され、読み出し障害を削減することが示されたとするほか、素子サイズの違いが障害の削減効果に与える影響調査から、どのサイズの素子でも磁化反転のしきい値電流は高く、読み出し障害の低減が確認されたとした。

いずれの材料パラメータ、素子形状でも、提案方式のディスターブ低減が確認され、磁化反転電流としては、従来方式よりも10倍程度のディスターブ低減が可能になったことから、これらの調査結果が、メモリセルデザインの指針となるとするほか、提案方式のディスターブ低減の際に自由層に発生していた磁化渦を含む磁化状態から、自由層の左右の磁化にスピン流が作用して磁化渦を挟んで磁化が拮抗し合うことでディスターブ低減が起こっていることも判明したとする。

加えて、実際のアレイ構造ではビット線とソース線の両方に電流を流すことになるため、メモリセルの場所によって電流パスの抵抗が異なることの影響が調べられたところ、1000個程度までは共通の配線に接続しても十分なディスターブ低減を得られることも明らかになったとしている。

なお、SOT-RAM固有の課題を見出し、なおかつ解決案を提示した今回の研究は、SOT-RAMの製品化に必須の技術であり、今後の応用が期待されるとしている。

今回の研究内容がまとめられた動画「SOT-RAM:持続可能なコンピューティングのための信頼性に優れた磁気メモリ」。再生時間:4分49秒。(YouTube東京理科大学チャンネル)