次に性能評価の結果がいくつか示された。まずは同じプロセスノード・同じ動作周波数でCortex-A57とCortex-A72を比較したもので、項目によって当然差はあるが、最低でも16%、最大で50%もの性能差があるとする(Photo12)。次が興味深いのだが、サーバ向けとしてXeon/Xeon Dとの比較である。まず20Thread同士の比較と言うことで、SPECint_rate 2006の結果がPhoto13である。

|

|

|

|

Photo12:テスト内容は下にある通り割と無難なものが多い。モバイル向けということで、GeekbenchとかAntutu、Minebenchなどが含まれているのが面白い |

Photo13:ARMのほうはRTLベースで1コアのシミュレーションを行い、これを20倍した模様だ |

2.3GHz駆動のXeon E5-2650 v3と2.6GHz駆動のXeon E5-2660 v3と、20コアのCortex-A57/A72を比較した結果(Photo13)であるが、まだHaswellには及ばないにしても、Cortex-A72ではかなり近いところに来ているというのがARMの主張である。実際には動作周波数が微妙に違うから同一周波数あたりの性能はもう少し開くことになるが、それでもHaswellコアの9割近い性能に収まると見られる。ただ、消費電力を比較した場合、Xeonが105W枠なのに対してCortex-A57/A72は30W未満で稼動できるとしており、これを考慮すると、消費電力あたりの性能やダイサイズあたりの性能では圧倒している、というほうをむしろ強調したいようだ(Photo14)。

|

|

|

Photo14:この30Wの数字にはCCN-508なども加味されているとする。もっともXeonの方もTDPが105Wだからといって本当にフルに105W使っているわけでもないので、差はもう少し小さいかもしれないが |

ただこの比較だと、Intelのほうは22nmノードなので公平ではない、という見方は当然ある。それもあってか、14nm世代のBroadwellコアとの比較も示された。まずダイサイズであるが、Cortex-A72は16nm FinFET+で大体1.15平方mmで、Broadwellコアの7分の1ほど。Broadwellと同じ8平方mmだと、4コアのCortex-M72に2MBの共有L2キャッシュが搭載されるとする(Photo15)。このBroadwellコアをベースにしたXeon Dとの比較にあたって、スペックとしてARMが提示したのがこちら(Photo16)。

|

|

|

|

Photo15:Broadwellの方はコアにL2まで含まれるので、それを加味すると1コアあたりの面積比はもう少し差は縮まる様にも思われる |

Photo16:これは「Xeon-D 1540」のものである。 |

これと比較するにあたり、まずはLenovoのYoga 3 Pro(Turbo時2.6GHz駆動)とDell Venus 11 Pro(Turbo時2GHz駆動)の2つの製品を使い、動作周波数と消費電力の関係を調べた結果がこちらである(Photo17)。Turboをフルに利かせるとそれなりに消費電力が増えるし、こまかくThrottlingが入るのはやむをえないところであるが、2GHz駆動ならコアあたり4W(パッケージ、つまり周辺回路も含むと5W)、2.6GHz駆動だと7W程度という測定結果を得ている。これを元に、2GHz駆動のCore-Mと、2.5GHz駆動のCorte-A72コアの推定値と比較したのがこちら(Photo18)。ものによって性能差はあるが、概ね20%未満といったところで、そう悪い数字ではない。特にMulti-Threadの場合、同じ4Wの枠内でCortex-A72は4コアをフルに使えるので、結構な性能差になっており、高密度サーバなどには適しているという見方は十分可能だ。

|

|

|

|

Photo17:これをどうやって調べたか、という話はまた改めて |

Photo18:同一周波数に揃えればCortex-A72の性能はもっと下がることになるが、同一消費電力枠にすればCortex-A72は更に性能が上がるわけで、その意味では大体コア(というかThread)あたり1Wという枠での比較という方法論にもそれなりの説得力がある |

実際にはまだCortex-A72を実装した製品が存在しない(早くて年末であり、特にサーバ向けは2016年以降になるだろう)から、これはあくまで参考値でしかないが、ARMがこの分野にそれなりのシェアを獲得できると踏んでいる根拠の1つがこの性能の高さ、という事は理解できる。

最後にそのサーバ向けの話を。ネットワークの帯域はどんどん増えており、これにあわせてサーバやルータなどを増強していかなければならないのはすでに周知の事実であるが(Photo19)、これをなるべく低いコストで抑えるためには効率性を引き上げる必要がある、というのがARMの主張である。ここにもう1つ、フレキシビリティが必要とされる、というのもトレンドであると同社は説明する(Photo20)。

|

|

|

|

Photo19:特にOPEX(Operation Expense:運用コスト)は事実上電気代な訳で、なので性能を落とさずにどうやって消費電力を下げるか(or電気代を増やさずにどうやって性能を上げるか)が鍵になる。もちろん両立できればそれに越したことは無い |

Photo20:この主張そのものはさして目新しくない |

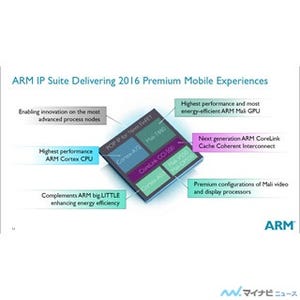

要するに小さなネットワークから大きなネットワークまで、同一のアーキテクチャでスケーラビリティを持たせる事が求められているという話だ。そこでARMは、Cortex-A7からCortex-A72まで、スケーラビリティを維持しながら複数の製品を提供することが出来るとする(Photo21)。実際、CCI-512を利用した場合、最大12 Cluster(48 core)の間でキャッシュコヒーレンシを取ることができるから、40コア以上の構成となるプロセッサを構築することも現実的であるとする(Photo22)。もちろんARMそのものがNetworkプロセッサを構築するわけではなく、あくまでスケーラビリティを持った製品を提供するという話で、これに沿ってInterconnectも2コアから48コアまで対応しており(Photo23)、あとは企業がどのInterconnectにどのコアを組み合わせるかを自由に選べる、としている。

|

|

|

|

|

Photo21:今さらCortex-A57でもという気はするのだが、これは「すでにCortex-A57を搭載したNetwork Processor製品が市場に出ている」からとの事。つまり既存のCortex-A57ベースの製品はMid range向けとなり、今後はCortex-A72をベースにハイエンド向けに製品展開が出来る、という意味となる |

Photo22:実際Cavium NetworksのThunderXシリーズは最大48コアの製品をラインアップしており、これは無茶な事例ではない。というか、実際の製品からこの模式図を作った感すらある。もっともCaviumの場合はCCI-500シリーズではなく独自のInterconnectを使っているのでそのままという訳ではないが、48コアはそう大げさではない。EZ-Chipsの100コアのTILE-Mxに比べればまだ控えめといっても良いかもしれない |

Photo23:ちなみにCCI-400もCCI-500/CCN-500もプロセッサに対するI/Fは共通なので、任意のコアを組み合わせることができるという話だった |

これまで、ARMはサーバマーケットに対して意欲は見せつつも、実際のソリューションとしては負荷の軽い用途向け、という形で遠慮がちなアプローチだったが、Cortex-A72とCCI-500シリーズの組み合わせで本格的にヘビーロードなサーバ向けにも進出できる準備が整った、と考えているようだ。本格的に動きが見えるのは2016年以降になるだろうが、結構な激戦になりそうな予感がする。