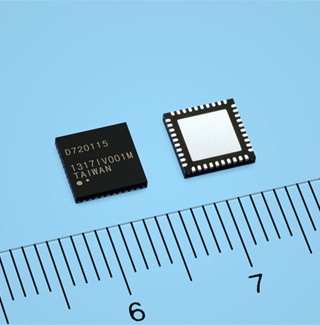

ルネサス エレクトロニクスは6月18日、LSIとそれを実装するプリント基板間のインピーダンス差(インピーダンス不整合)により生じる信号波形の悪化を防ぐことを目的として、一般的なBGAタイプのパッケージ基板内に、複数種類の「分布定数回路」を3次元的に組み合わせることで、信号伝送速度を向上させつつ、従来比3倍の信号配線密度を実現できる設計技術を開発したことを発表した。

同成果の詳細は、パッケージ技術に関する国際学会「The 13th International Conference on Electronics Packaging (ICEP 2013)」にて発表された。

従来、12.5Gpbsクラスの速度に対応するためには、チップの各入出力チャネルにコイルを1個ずつ付加してインピーダンス整合回路を構成し、インピーダンスの差を縮めるといった手法が考えられてきたが、チップが大きくなり製造コストが高くなるほか、チップサイズの拡大防止のために、微細プロセスでコイルを作った場合では、静電ノイズ耐性が低下するという課題があった。

今回開発された技術は、複数種類の分布定数回路を密充填と成るように配置することで、信号速度の高速化と高密度化を同時に実現したもの。具体的には、12.5Gbpsを超える広い信号帯域を確保するために分布定数回路を多段構成としたほか、スルーホールまたはビアで構成された大きさの異なる2種類の分布定数回路を、パッケージ内で層を分けた上で、互いの隙間を埋める様に配置する事で、密充填構造を実現した。

また分布定数回路では、信号の位相差が360度毎に同じ特性を有することを利用して、分布定数回路の分散配置を行い、およそ従来比3倍の信号密度と2倍の信号帯域をもつ分布定数回路を得ることに成功。

これにより、チップ内への回路追加や、パッケージ基板への特殊な追加加工を付加することなく、既存のパッケージ構造上でOIFが標準化した-8dB以下の許容信号反射量規格をクリアしたという。

さらに同社では、同技術を用いたパッケージ設計を効率よく行うための設計環境として、ビア、スルーホールおよび配線などを、3次元形状の分布定数部品としてライブラリ化しており、パッケージ基板の配線設計を行う際にこれらのあらかじめ準備された3次元形状の分布定数部品を活用することで、従来の電磁界解析を行いながら設計する手法と比較して、1/1000以下の時間で行うことが可能になるとしている。

なお同社では、今回の開発した設計技術を12.5Gbpsから25Gbpsクラスの基幹ネットワーク向けだけでなく、今後登場するPCI Express version4などの16Gbpsクラスのデータ通信を行う通信規格にも応用可能なものと考えているとのことで、積極的に同技術の応用製品の品種拡充を推進していく計画としている。