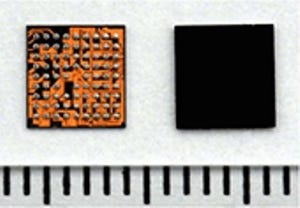

東芝は2月14日、従来のゲートアレイのようにメタルマスク層をカスタマイズするだけで、短期間で試作サンプルを提供できる新ストラクチャードアレイ製品の販売を開始したと発表した。

米BaySandからライセンスを受けた技術を使用し、数枚のメタルマスク層をカスタマイズすることで高機能、高性能、低消費電力のSoC製品を実現することが可能なデバイスで、FPGAとの互換性を持っているため、FPGAで検証済のRTLの設計データがあれば、従来のASICに比べて1/5の短期間(5週間)で試作サンプルを提供することができるという。また、その際、FPGAと同じピン配置の試作サンプルを提供することも可能だという。

さらに、カスタマイズするメタルマスク層を数枚に抑えることにより、開発費を大幅に削減することもできると同社では説明する。

2013年4月より65nmプロセス製品の量産に対応する予定で、今後、40nm以降のプロセス製品も順次製品化していく予定とするほか、高速トランシーバを搭載した製品ラインアップも各プロセスにおいて開発を計画しているという。

なお、製品の主な仕様は以下の通り。

- プロセスノード:65nm

- 回路規模:最大30Mゲート

- 搭載SRAM:最大20Mビット

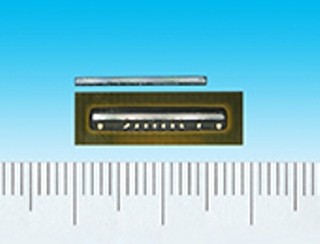

- I/Oピン:最大1200I/O

- LVDSやDDRにも対応可能

- デザイン受け:対応中