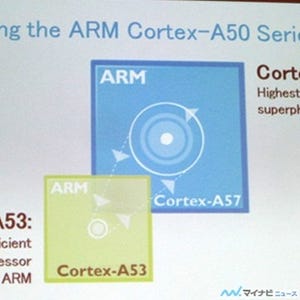

ARMとCadence Design Systemsは12月20日(米国時間)、ARM Cortex-A7コアを搭載した14nmプロセス採用テストチップがテープアウトしたことを発表した。

同チップは、CadenceのRTLからサインオフまでを完全に網羅した設計フローを用いて、Samsung Electronicsの14nm FinFETプロセス向けに開発されたもので、Cadenceの「Encounter RTL Compiler」、「Encounter Test」、「Encounter Digital Implementation System」、「Cadence QRC Extraction」、「Encounter Timing System」および「Encounter Power System」を含む「RTL-to-signoff統合フロー」を用いて実現された。

Cortex-A7のほか、ARM Artisanスタンダードセル・ライブラリ、次世代メモリおよび汎用I/Oを搭載しており、両社では、今回に成果について、ARMプロセッサコアを搭載したSoCをFinFETテクノロジ上で実現するためのシステマティックなプログラムの一環として達成されたもので、次世代の携帯機器において、低消費電力をリードしていく上で重要なものになるとコメントしている。