東芝は20日、IBMと共同で高駆動力を実現したCMOSFETを開発したことを発表した。

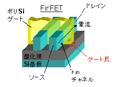

同技術は、結晶方位として(100)面と(110)面の2つの異なるSi層を接合した基板(DSB基板)を用いたもの。従来のDSB基板は、ホール移動度の向上により、PMOSFETの駆動力が改善する一方、NMOSFETでは電子移動度が低下し、駆動力が劣化してしまう問題があった。

今回、開発された技術では、(100)面のSi層を45°回転させて結合することで、漏れ電流に影響を与えるとされるNMOSFETとPMOSFETの境界で発生するDSB基板特有の結晶欠陥のサイズを低減した。

また、改良を施したDSB基板でのPMOSFETのホール移動度は(110)面Si膜厚に依存することから、膜厚の異なる3種類の改良型DSB基板の電気特性を比較することで、(110)面のSi層を薄膜化した基板がより高い駆動電流を示すとともに、接合容量も低減されることを確認した。

これにより、リングオシレータを試作。Si基板を用いた場合と比較して30%の高速化、従来のDSB基板を用いた場合と比較しても10%の高速化が確認され、NMOSFETの駆動力を低下させることなく、高い駆動力を持つPMOSFETを作製することが可能なことを示した。