産業技術総合研究所(産総研)などは5月16日、次世代の不揮発性メモリであるとされる磁気ランダムアクセスメモリ(MRAM)の3次元積層プロセス技術を開発したと発表した。

同成果は、産総研スピントロニクス研究センター金属スピントロニクスチーム 薬師寺 啓研究チーム長、集積マイクロシステム研究センター 高木秀樹総括研究主幹、ウエハレベル実装研究チーム 倉島優一主任研究員、ナノエレクトロニクス研究部門3D集積システムグループ 菊地克弥研究グループ長、渡辺直也主任研究員らの研究グループによるもので、5月15日付けの国際科学誌「Applied Physics Express」に掲載された。

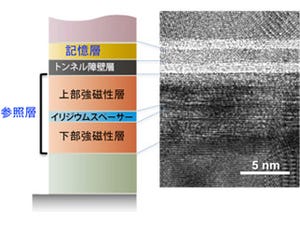

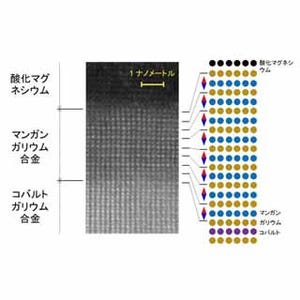

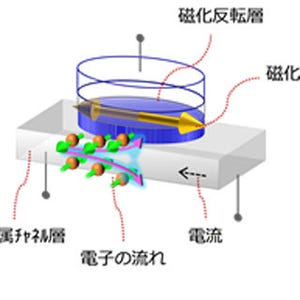

MRAMは、垂直磁化TMR素子をベースとする記録ビットと、ビット選択に用いる半導体トランジスタ(CMOS)、多結晶銅などの金属配線からなり、通常、垂直磁化TMR素子薄膜(TMR薄膜)は、逐次積層といってCMOS形成後に金属配線上に直接形成される。MRAMの大容量化には、原子レベルの不均一性や凹凸によるTMR薄膜のバラツキ抑制、材料の選択が重要となるが、多結晶銅配線上へのTMR薄膜形成ではバラツキ抑制や材料の選択肢には限界があった。

今回、同研究グループは、CMOS形成ウェハとTMR薄膜ウェハを別体形成した後に圧着して接合する、3次元積層プロセス技術によるTMR素子の作製に成功した。なお、今回の研究ではCMOS形成ウェハを銅電極形成ウェハで代用している。

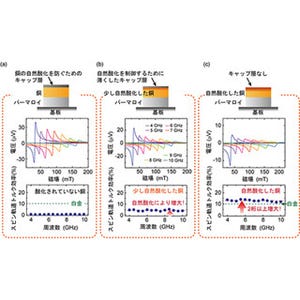

同3次元積層プロセスにより、ウェハ上に銅電極層、タンタル接合層、多結晶TMR薄膜層の順に形成された3次元積層試料に微細加工を行い、サイズが28nm~65nmのMRAMデバイスを作製し、動作を確認したところ、3次元積層プロセスを行わないTMR薄膜を用いたMRAMデバイスと比較して、3次元積層プロセスを経た後のMRAMデバイスは、読出性能・書込性能はまったく劣化せず、STT-MRAMで重要な性能指標となる「データ書き込み効率」は2に達し、世界トップクラスの性能を維持していたという。

今回用いた多結晶TMR薄膜よりも単結晶TMR薄膜の方が機械的強度が強いことから、今回の3次元積層プロセスは単結晶TMR薄膜にもそのまま適用できると考えられ、同研究グループは現在、単結晶TMR薄膜の開発を進めているとしている。今後2年以内に単結晶TMR薄膜とCMOSウェハの3次元積層プロセスを確立し、5年以内に3次元積層MRAMの製品開発の着手を目指していきたい考えだ。