Broadcomは12月5日、都内で会見を開き、同社が10月15日(米国時間)に発表した64ビットARMコアを採用したARMv8-Aマルチコアプロセッサアーキテクチャデバイスに関する技術解説を行った。

同デバイスは、NFV(Network Functions Virtualization)向けに開発されているもので、高性能が要求されるサーバクラスの性能を実現することができるアウトオブオーダーサポートのスパースカラーエンジン、クワッドイシュー、クワッドスレッドなどを採用しているほか、TSMCの16nm FinFETプロセスを用い、動作周波数3GHz以上を実現しようというもの。

同社のマルチコア通信プロセッサが対象とする市場は30億ドル規模。主に4つのセグメントがあり、ストレージが10億6000万ドル、ワイヤレス基地局が6億8000万ドル、ルータやスイッチなどのネットワーキングが12億6000万ドル、そしてセキュリティが2億7000万ドルとなっているが、セキュリティ分野は市場規模は小さいが伸び率が一番高く、今後の成長が期待できる分野とする。

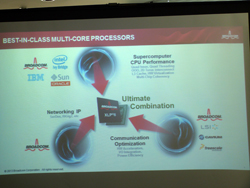

こうした市場分野に対し、同社としては「スーパーコンピュータクラスのCPUパフォーマンス」、「通信分野に向けた各種の最適化技術」、そして通信分野に特化したさまざまな「ネットワークIP」の3つを組み合わせることで、優位性を確保しようというのが今回の次世代デバイスの目指すところ。

|

|

3つの特徴を持つ次世代NFV向けマルチコアプロセッサ。ここの「Communication Optimization」で語られているハードウェアアクセラレータは、DPIエンジンとか暗号化エンジンとか、多数のエンジンを指しており、それぞれの用途に対し高速処理を可能とする |

|

|

Broadcomでプロセッサーズ&ワイヤレスインフラストラクチャのシニアディレクターを務めるクリス・オライリー氏 |

「今後の10年、20年先を考えると、ネットワークの進化において明らかなことの1つは、携帯機器の活用が進み、ネットワークの負荷が増えていくことだ」と語るのは、同社プロセッサーズ&ワイヤレスインフラストラクチャのシニアディレクターを務めるクリス・オライリー氏。

また、「携帯機器に加え、今後はIoTの普及や、リッチメディアコンテンツの利用増加、携帯機器の機能向上によるサービスの変化、ビッグデータとクラウドコンピューティングの活用といったこともあり、ネットワークにはより多くの負荷がかかることとなる」とし、その対応のためには、ネットワーク上に1つの端末からどういったパケットデータが流れており、その中で優先しないといけないものは何か、といったことをインテリジェントにリアルタイムで処理することが可能なプロセッサが必要になるとする。「ネットワーク上でやり取りされている各種のデータの重要性を瞬時に判断し、それらをセキュアな状態で保持し続ける必要もある。また、そういった複雑な処理をしながらも、低消費電力も維持しなければならない」と非常にチャレンジングなことだとしながらも、現在開発を行っている次世代マルチコアプロセッサでは、そうしたニーズに対応可能だとする。

また、今回ARMv8アーキテクチャを採用したデバイスとしたことで、「ARMの持つエコシステムをユーザーは活用することができるようになるほか、既存APIを活用しつつ、対象範囲の拡大や性能向上を図ることが可能になる」とするほか、Broadcom側としても「ARMのエコシステムとしてNFV向けソフトウェア環境の提供を進めることで、より多くのカスタマに次世代チップを活用してもらえるようになる」としており、ARM用Linuxカーネルを開発する非営利組織「Linaro」などとも連携を進めることで、さらなる利用拡大を図っていくとする。

|

|

|

次世代マルチコアプロセッサで用いられるアーキテクチャの概要。今回用いられる64ビットARMコアは公開されているCortex-A57/A53ではなく、アーキテクチャそのもののライセンスで、Broadcomにて、カスタマイズしたコアとして活用される形となっている |

現在同社が提供しているMIPS64アーキテクチャベースのXLP900から次世代プロセッサはARMv8アーキテクチャへと変更されることとなる |

なお、ファウンドリであるTSMCの16nm FinFETプロセスは2013年中の量産(先行量産/リスク量産)を開始する計画で、2014年にはすでに一部のデバイスベンダの製品が出荷される見込み。Broadcomとしても、それなりの時期に提供を開始したいとしており、そう遠くないタイミングで製品提供ができる見通しであるとしている。