ARMは、2015年2月に発表した2世代目の64bitプロセッサ、Cortex-A72の内部アーキテクチャなどを公開した。Cortex-A72は、ARMv8と呼ばれる64bitプロセッサで、従来の32bit CPUであるARMv7アーキテクチャを含み、さらにモード切替で64bit CPUとして動作する。Intel系のx86/x64と違い、64bitモードの命令セットは、新たに設計されており完全に32bitとは別になっている。

|

64bit用のARMv8アーキテクチャは、AArch32とAArch64の2つのモードを持ち、AArch32は従来のARMv8完全互換の32bitモード、AArch64は新しい命令セットをもつ64bitモード |

ARM系のプロセッサは、大きく3系統あり、スマートフォンやサーバーなど、仮想記憶を持つコンピュータシステムとして使うことを想定したのが「A」系列(製品名としてはCortex-A)で、そのほかにリアルタイム処理向けの「R」や組み込み向けの「M」などがある。

Cortex-A系列には、大きくエネルギー効率を重視したCorex-A5/A7/A53と、性能を重視したCortex-A72/A57/A17/A15がある。なお、性能重視した製品でも、製造プロセスを変えることでモバイル向けとサーバー向けを作り分ける。

また、ARM系のプロセッサは、シングルコア、マルチコアといった構成に加え、さまざまな周辺回路などを統合した「SoC」(System On a Chip)として作られ、そのために、メモリコントローラーやGPU、周辺回路と接続するための内部接続技術として「CORELINK」がある。このCORELINKにもプロセッサコア数などに応じていくつかの種類があり、一般的にはこれらを組み合わせてSoCを構成する。

Cortex-A系列のプロセッサは、このCORELINKとの組み合わせにより、L3キャッシュやメモリコントローラー数、最大マルチコア数などが変わってくる。現在のCORELINKは、小規模な用途からサーバー向けSoCまで対応が可能なラインアップになっている。

Cortex-A72は現在、プロセッサの基本的な設計が完了し、半導体製造を請け負うファウンドリ各社や自社で製造ラインを持つ半導体メーカーが自社の製造プロセスに適合させるべく、最適化などの作業を行っている最中だ。

実際の製品は、ファウンドリーや半導体メーカーが自社プロセスへの適合を行い、そのうえでSoCとして製造を行う。セットメーカーは、これを利用して製品を作るという流れになり、現時点では、2016年頃には製品が登場するのではないかと思われる。

設計したARMによれば、Cortex-A72は、14または16nmプロセスでの製造が想定されており、モバイル向けに製造した場合、最大クロック周波数は2.5GHz程度で、現在市場に出ているCortex-A15の3.5倍程度の性能を持つことになるという。なお、第一世代の64bitプロセッサであるCortex-A57では、現在の20nmメートルで製造された製品はA15の2倍程度とされている。

また、Cortex-A15は28nmでの製造であり、これとA72を同じ処理負荷で比較すると、28nmプロセスで製造した場合でも50%の消費電力であり、16nmプロセスでの製造であれば75%も消費電力を減らすことが可能だという。

また、低消費電力のプロセッサと組み合わせ、処理負荷により、プロセッサを切り替える「big.LITTLE」技術を使うと、さらに40~60%消費電力を下げることが可能になるとしている。

Cortex-A72は、消費電力の削減についてはもちろんだが、シングルスレッド性能を重視して設計されたという。モバイル向けのアプリケーションプロセッサでは、ユーザーが利用するアプリケーションで見た場合、やはりシングルスレッド性能が大きく影響する。また、サーバー用途でもシングルスレッド性能は重要になる。

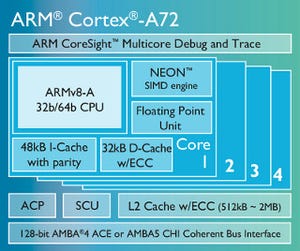

Cortex-A72は、コア間で共有するL2キャッシュ(512KBから4MBまでの構成が選択できる)と、命令用、データ用に分離されたL1キャッシュ(命令用48KB、データ用32KB)がある。パイプラインは、以下の図ようになっていて、命令フェッチ、デコーダー/リネーム、命令ディスパッチ/リタイアと実行ユニットとなっている。

また、命令フェッチユニットには、分岐予測機構が付随しており、ここで分岐命令の予測を行う。なお、A72ではプログラム内部のループなどに使われる分岐先が比較的近くにある分岐命令の予測に対して最適化が図られている。

次のデコーダ/リネームでは、32bitのAArch32命令(ARMv7命令)や64bitのAArch64命令を内部的に利用するμOPSに変換する。以後の処理は、動作モードがどちらでもμOPSを実行することになる。

リネームとは、命令で指定されているレジスタ番号を物理レジスタ番号(アウトオブオーダー機構を持つCPUで、アーキテクチャ上のレジスタよりも多くの物理レジスタを持つ)に変換する機構。これにより、データに関連性はないが、同じレジスタを使う2つの命令を順番に関係なく実行させることが可能になる。

ディスパッチ、リタイアは、後続の実行ユニットに対して命令を発行し、その終了処理を行う部分。ここは、同時5命令の発行が可能になっている。従来のA57では3命令だけだった。

実行ユニットは、「シングルサイクル命令用」、「分岐処理」、「複数サイクル命令用」、「浮動小数点/SIMD演算」、「ロードストア」の5種類あるが、このうち、「シングルサイクル」、「浮動小数点/SIMD」、「ロードストア」のユニットは、命令を受け入れるポート数が2つがあり、同時に2命令を処理できる。

各実行ユニットの性能も向上しており、たとえば整数命令では、CRC演算命令が1サイクルで実行可能(従来は3サイクル)になっていたり、割り算命令の実行サイクルが半分になっている。浮動小数点演算でもサイクル数が削減されているなど、実行性能が向上している。

ロードストアユニットは、メモリの読み書きを行う場合のアドレスを計算するなどの処理を行うが、こちらはロード用が1ポート、ストア用が1ポートで、最大2つの演算を並列に行える。また、L1、L2キャッシュのデータのプリフェッチ(命令の実行前にキャッシュをアクセスしてデータ読み込み処理を行うこと)機能もある。

L2キャッシュがメモリにアクセスする場合、命令コードで指定されている仮想メモリアドレスを物理メモリアドレスに変換する必要があるが、そのためのMMU(メモリ管理ユニット)のアドレス変換機構が高速化されていたり、TLB(Translation Look-ahead Buffer)仮想アドレスの変換結果を保持しておいて、アドレス変換を繰り返し行うことを避けて高速アクセスを可能にする)の読み出しサイクルを短縮している。

マルチプロセッサの場合、他のプロセッサによるメモリへの書き込みなどで、それぞれが持つキャッシュ情報を常に一貫性(Coherence)のある状態へ保つ必要がある。このための機構としてCortex-A72はACP(Accelerator coherence port)を持つ。A72では、より高速なCORELINKに対応するため、この部分にも強化が行われている。

|

Cortex-A72は4コアで1つのクラスタを構成して、L2キャッシュはクラスタ内で共有し、ほかにもクラスタが接続されるマルチプロセッサ構成の場合、他のクラスタやGPUなどの周辺機器側からのメモリアクセスに対して、キャッシュの一貫性を保つためのACPを持つ |

ARMによるパフォーマンス予測では、Cortex-A72は、A57に比べて、1.16~1.5倍程度の性能向上があるという。Cortex-A57は、最初の64bit実装でもあり、実際には、それほど性能が高くないといわれている。Cortex-A72は、全般的に性能を向上させており、メモリ空間の増大などとあわせ、これを利用したシステムは高い性能が出せるようだ。