2012年2月16日に開催された理化学研究所(理研)シンポジウムにおいて、東京大学(東大)情報基盤センター長の石川裕教授が基調講演を行い、その中で、石川教授の私案という位置づけであるが、東大のPost T2KスパコンではIntelのMany Integrated Core(MIC)プロセサの採用を検討していることが明らかにされた。

|

|

理研シンポジウムで基調講演を行う石川教授 |

東大 情報基盤センターは、メーカー製品である市販のスパコンを設置するシステムと、東大の研究的要素を入れたシステムという2種類のスパコンを持っている。メーカー製品のスパコンの系列は、POWER5を使う日立製作所のSR11000システムが使用されていたが、今回の更新で、富士通の「京」の製品版である1.13PFlopsのFX10システムを採用し、2012年4月稼働を目指して準備が進んでいる。また、54.9TFlopsのPOWER7ベースの日立のSR16000/M1も併設される。

一方、研究要素を持つスパコンは、2008年に筑波大学、京都大学と共通仕様を作成して調達したT2K(Tsukuba、Tokyo、Kyoto大)スパコンが使われている。仕様は共通であるが、メーカーは異なり、筑波大は米国のAppro、東大は日立、京大は富士通がT2K仕様に基づいて開発したマシンを使っている。

東大の現用のT2Kスパコンは日立のHA8000を使う140TFlopsのシステムであるが、2013年から2014年ころには更新時期を迎える。当然であるが、東大は、この更新ではどのようなシステムを作るのかという検討を進めている。

次回の更新では40~100PFlopsの性能を目指すが、現状の検討で見えているのは40に近い方の数字であるという。

この性能を実現するにはFlops/Wのエネルギー効率の観点から、汎用プロセサだけでなく、メニーコアのプロセサを主体とすることが必須であるが、このメニーコアシステムの接続形態にも色々なバリエーションがある。

図の左上の形態は、メニーコアプロセサ(GPGPUやIntelのMICを指す)を搭載した複数のボードをPCI Expressで汎用CPUを載せたホストボードに接続するというもので、東京工業大学(東工大)のTSUBAME2.0などはこの形態である。左下はメニーコアのエンジンを汎用プロセサに統合し1チップにした構成で、IntelのSandy BridgeやAMDのAPUがこれにあたる。これらの図の左側に書かれた形態は、アクセラレータの性能はともかく、現在、市販品として存在する形態である。

右上の形態はメニーコアのプロセサが汎用プロセサとバスで直結しているという形態で、現在は製品がない。右下はメニーコアのプロセサだけでシステムを構成するもので、これも現在は製品はない。

Post T2Kシステムでは大規模データ解析と数値計算の両方のアプリケーションをカバーする必要があり、浮動小数点演算能力だけでなく、I/O性能も重要なポイントである。また、多数のプロセサコアを使うシステムである、並列性能が十分に発揮できる構成であることが要件である。

この要件を満たすシステムとして、Post T2Kスパコンでは、演算性能主体のメニーコアユニット群をホストプロセサ群が囲む形をとり、メニーコア群が浮動小数点演算を担当して、汎用プロセサ群がディスクI/Oやプロセサノード間の通信を担当するという処理分担を考えている。そして、各計算ノードは1つのホストCPUユニットに4つのメニーコアユニットがPCI Expressなどで接続され、そこにSSDやインタコネクトのインタフェースユニットも繋がっているという図になっている。他の計算ノードやファイルシステムは、このインタコネクトを経由して接続される。

このようなハードウェア構成のPost T2Kスパコンのソフトウェアであるが、メニーコアのハードウェアの上にはAALと書かれたAbstraction層、カーネル間の通信を担うIKCL層、そしてOSに基本的なシステムサービスを提供するSMSL層がある。メニーコアを制御するホストプロセサ側にもメニーコアプロセサを制御するデバイスドライバと、メニーコア側のそれぞれの層に対応する機能層が組み込まれる。

図の左側のホストプロセサとは別個のメニーコアプロセサを使う構成では、両者はPCI Expressで接続されるが、メニーコアが汎用OSを走らせる機能を持っている場合は、右側の図のように両者をメニーコア上で走らせることもできる。

この時、問題になるのがメニーコアプロセサ間の連携である。

NVIDIAのGPUではGPU Directと称してGPU間でメモリの直接転送が可能であるかのように宣伝しているが、このDirectは1つのPCI Expressに接続されたGPUメモリの間の話で、InfiniBandなどで接続された別の計算ノードのGPUのメモリ間では、直接のデータ転送はできない。このような転送では、それぞれのGPUが接続されているホストプロセサのメモリにデータ転送し、ホストプロセサがInfiniBand経由で相手方のホストプロセサのメモリにデータ転送し、そこから最終目的地であるGPUのメモリにデータ転送するという手順が必要である。

これは、GPUはPCI Expressに接続されているが、PCI Expressの動作を指定できるルートデバイスではなく、直接、InfiniBandのネットワークインタフェースカード(NIC)を制御することができないという構造になっているからである。ホストプロセサが、通信やDMAを行うNICを制御するアドレスをメニーコアプロセサに教えてやり、メニーコアプロセサがNICを直接制御できるという構造にすれば、このようなオーバヘッドの大部分は解消する。

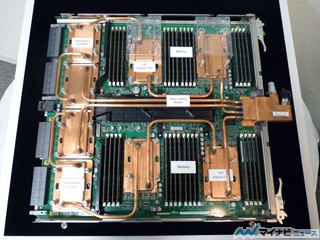

そうすると、メニーコアプロセサのメモリから両側のホストプロセサを経由せず、InfiniBand経由で相手方のメニーコアプロセサのメモリへのDMA転送が可能となる。このような動作ができるメニーコアプロセサとして、現在、製品化が見えているものはIntelのメニーコア(MIC)のKnights Cornerである。このため、東大ではIntelのメニーコアの開発システムであるKnights Ferryを使ってPost T2Kで必要となる基本ソフトウェアや通信コンポーネントなどのソフトウェア開発を進めているという。