Nehalem

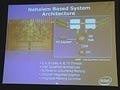

次にNehalemに関してだ。Otellini氏の基調講演でウェハ(Photo22)やダイ写真(Photo23,24)が公開され、さらにこれを用いた16Threadsでの動作デモも示された(Photo25)。またPress ConferenceではSmith氏が実際にダイに搭載したNehalemとサポートチップセットを示した(Photo26~28)。そのNehalem、「詳細は2008年まで待て」(Smith氏。Press向けRound Tableの最初の挨拶がこれだった)ということで、MicroArchitectureに関しては何も語られていないのが現状ではあるが、CSIことIntel QuickPath Atchitectureを使い、2P(Photo29)や4P(Photo30)の様な構成が簡単に取れる事を明らかにした。これに関してGelsinger氏(Photo31)は「マクロで見ると、Opteronと何も違いはない。ただ細かく見ると、メモリはDDR3世代でより帯域が広くなるし、Intel QuickPathはさらに柔軟に構成を変えられ、しかも高速・Low Latencyである。全ての部分でIntelの方が優れている」と、この手の質問には割にSensitiveであることを伺わせるものだった(*2)。

|

Photo22:300mmウェハで、横が最大15個、縦が最大22個ほど取れるように見える。ここから見ると、ダイ寸法は20mm×13.6mmといったところだが、実際には切りしろもあるからもう少し小さいと思う。 |

Photo23:随分横長になった印象。このプレゼンテーションから見るダイ寸法の比率は縦:横が1:1.45といったところ。ちなみに総トランジスタ数は7億3100万と発表されている。 |

|

Photo29:2P構成。2つのCPUから直接I/O Hubに繋がるところがOpteronと異なるあたりか。 |

Photo30:なんというか、Opteronの4Pそのもの。K8世代はHTLinkが最大3本だったが、Barcelona世代(というか、正確にはShanghai)からは4本に増えるので、こうなると何も変わらないという印象も。 |

さてPhoto29・30ではMemoryが2chになっているが、実際はMemory Busが3chであることが確認された。というのは3倍の帯域と称しているためで、DDR2の2chからDDR3の3chとなることで、速度そのものが2倍(DDR2→DDR3)で、チャネル数が1.5倍(2ch→3ch)という訳だ。問題はこの3chが従来同様に同期して動くのか、それとも(BarcelonaやGriffinの様に)非同期に動作するのかは現在不明である。ちなみに3chとなった理由については「BandwidthとCapacityの問題である」(Gelsinger氏)とした。このあたりはバランスの問題であり、4P程度までの構成であれば、3chでBandwidthとメモリ容量、ピン数もう一つはFB-DIMMの扱いである。Nehalem世代ではDDR3のみのサポートで、DDR2のサポートは無いとGelsinger氏も明言したが、ただそうなった時に(Photo29の)"Buffer DIMM"が何を指すかということになる。上で書いたとおりDDR3世代のFB-DIMM2は事実上なくなったとみなされているが、Gelsinger氏は「我々はBuffered Memoryをサポートする」と繰り返しており、事実上Registered DIMMに回帰するものと想像される。もっとも、Smith氏は「現在アナウンスしているNehalemではDDR3をサポートする」と但し書きをつけたり、「異なるセグメントには異なるメモリアーキテクチャが必要になる。High-End ServerにはRASの機能とか大きなメモリ容量が必要になる。たとえばItaniumのレベルのサーバーには、大容量のメモリが必須だろう」という表現で、かろうじて現世代のFB-DIMMを使う可能性に含みを残してはいたので、このあたりはまだ確定ではないのかもしれないが。

その他に明らかにされたこととしては、

- Nehalemは2008年後半、まずServer/WorkstationとHigh-End Desktop向けに投入される。Mobileに関しては、Mooly Eden氏は否定はしなかったが、時期が2008年中なのか、それ以降なのかは明らかにされなかった。

- 「MicroArchitecutureやPipelineも完全に再設計された。この結果、Nehalem世代は64bitにFull Optimizeされる。もちろん32bitに対しても同様だ」(Gensinger氏)としており、64bitでの制約が残ったCore Microarchitecureとは異なる事を強調した。

- SMTについては「そもそもSMTはエレガントな設計。Resource Reuseの観点から見ると、最小(4~5%)のダイの増加で、最低は0%だが最高だと30~40%の性能Gainがある。3~4way SMTはComplexityの観点で向かない。しかも非常にPower Efficiencyである。Power/Performanceの観点から見ても、SMTは良いアイディアだと思う」(Gelsinger氏)とした。

- Nehalem世代におけるSkullTrailの様なDual Graphics構成に関して「図2の様な構成は、理論上は可能だ。ただ実際にどうなるかはBoard Imprementationの問題で現時点では何ともいえない」(Smith氏)との話だった。

- Intel QuickPathは「Serial Bi-Directional Differential Signaling」(Smith氏)であり、またサーバー/デスクトップ/ワークステーションなど用途に応じて「いくつかのSpeed Option」があると述べた。

といったあたりで、美味しいところは来年のIDFまでお預けとなった。

(*2)後から出てくる製品が優れてなかったら勝負にならないわけで、現時点では優れていることは間違いないと筆者は思うが、ただこれもHT Link 3.0が登場するShanghai(開発コードネーム)以降でどうなってくるかはまた別の問題だと思う。加えて言うと、AMDは当然これをもって同社のDirect Connect Architectureの優位性(「我々の優れたアーキテクチャをIntelが真似した」云々)を宣伝すると予測できるわけで、暫くは宣伝合戦が煩いことになりそうだ。