大阪大学(阪大)と東京工業大学(東工大)は5月20日、STT-MRAMなどのスピントロニクスデバイスにおける低消費電力の新たな電圧情報書き込み技術に向け、高性能な「界面マルチフェロイック構造」を開発し、従来の2倍の値となる世界最高レベルの性能指標(磁気電気結合係数)を達成するとともに、電界印加による不揮発メモリ状態の繰り返しスイッチングを実証したことを発表した。

同成果は、阪大大学院 基礎工学研究科の藤井竣平大学院生(研究当時)、同・宇佐見喬政 特任研究員、阪大大学院 工学研究科の白土優准教授、東工大 物質理工学院 材料系の合田義弘准教授、阪大大学院 基礎工学研究科の浜屋宏平教授らの共同研究チームによるもの。詳細は、英科学誌「Nature」系の材料科学全般を扱うオープンアクセスジャーナル「NPG Asia Materials」に掲載された。

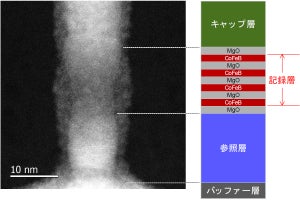

コンピュータの消費電力を抑制する不揮発メモリとして、磁気抵抗メモリ(MRAM)のうち、別の磁性体からスピン流を注入するスピン移行トルク(STT)方式が実用化されているが、STT-MRAMは、情報の書き込み時に電流を印加するためにジュール発熱によるエネルギー損失を伴い、書き込み時のエネルギー消費電力が大きいことが課題となっている。そこで、より消費電力を抑制できる書き込み方式として、さまざまな電界印加方式の技術開発が進められている。

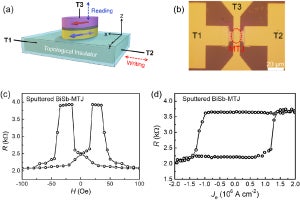

中でも最近注目されているのが、強磁性体(磁石)と圧電体の2層から構成される界面マルチフェロイック構造を利用した電界印加方式だという。これは、圧電歪みを強磁性体に伝播させることで、強磁性体の磁化方向を制御する手法だという。

また界面マルチフェロイック構造は、材料の組み合わせが豊富であり、室温を含む幅広い温度での動作が可能となるため、ほかの手法に比べてデバイス応用上の多くの利点を有している。

ただし実用化を目指すには、より小さな電圧で磁化方向を制御することができる界面マルチフェロイック材料の開発が重要とされており、このような材料の性能を表す指標の1つである磁気電気結合係数は、大きいほど小さな電界で大きな磁化の変化が発現することを意味する。界面マルチフェロイック材料の実用化のためには、10-5s/mを超えることが必要とされているが、これまで強磁性体としてスピン偏極率の高い物質を用いた場合、磁気電気結合係数は10-5s/m未満に留まっており、この壁を超えることは困難だったという。

さらに、これまでの研究では、磁気電気結合係数を10-5s/m台まで向上させるため、スピントロニクスデバイスに適用できない「磁歪材料」を用いた研究が多くなされてきたものの、応用上重要である「スピントロニクスデバイス用の磁石」を用いた高性能実証には至っていなかったという。

そこで研究チームは今回、スピントロニクスデバイス用の磁石として重要な指標である「高スピン偏極率」を有することが知られるコバルト系ホイスラー合金磁石の一種である「Co2FeSi」に着目。そして、高い圧電性能を有する圧電体「PMN-PT」と組み合わせることにより、高品質な界面マルチフェロイック構造の作製を試みることにしたとする。