1959年、物理学者のリチャード・ファインマンは、米国物理学会で行った有名な講演のなかで、「微小なロボットハンドを集積した原子サイズの工場」「原子1個1個を直接操作して微小な構造を形成したり、物質の新しい特性を引き出す技術」など、今日のナノテクノロジーの発展を予見したといえるさまざまなアイデアを提示した。この講演「There's Plenty of Room at the Bottom」のなかでファインマンは、「直径が原子10~100個分の配線を使い、1000オングストローム(100nm)程度の大きさに収まる回路からなる微小なコンピュータ」にも言及しているが、このようなナノスケールのコンピュータは現在もまだ実現していない。

カリフォルニア大学サンタバーバラ校(UCSB)の研究チームは、ファインマンの残したこの課題の実現を目指し、新構造のデバイスを設計した。その構造は、不揮発性メモリの一種である「メモリスタ」に論理回路としての機能も統合し、3次元構造化するというもの。通常のコンピュータでは分離されているデータ処理機能と記憶機能を同時に1カ所で行えるようにすることで、高速で微小なコンピュータが可能になるという。

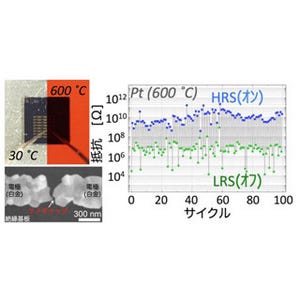

メモリスタは、酸化物半導体薄膜を用いた記憶デバイスであり、素子内を通過した電流の積分値(電荷)で抵抗が変化する性質を記憶の原理として利用する。記憶(メモリ)に抵抗(レジスタ)を用いることからメモリスタと呼ばれる。メモリスタの原理はカリフォルニア大学バークレー校のレオン・チュア教授が1971年の論文で発表し、その後、2008年になってHPが実デバイスの作製に成功していた。今回の研究を主導しているドミトリ・ストルコフ教授は、2008年当時のHPでのメモリスタ開発メンバーの1人である。

メモリスタは記憶デバイスであるだけでなく、低抵抗状態を論理状態「0」、高抵抗状態を論理状態「1」に対応させることで論理回路としても利用することができる。学術誌「Nano Research」に掲載された論文によると、研究チームは今回、メモリスタを用いた3次元回路における記憶動作と論理演算動作を実証した。3次元積層されたメモリスタによる半加算器の動作とマルチサイクル・マルチゲートでの実質含意論理演算を実験的に確かめたのは、今回が初であるという。

半加算器は、2進数1桁の加算を行う論理回路。下位の桁からの繰り上がりのある加算を行うには半加算器2個を組み合わせて全加算器を構成する。全加算器8個を使えば8ビット加算器が実現できる。3次元構造のメモリスタ論理回路によって、たとえば、全体が50nm×50nm×50nmサイズに収まる8ビット加算器が可能になるという。ストルコフ教授は「今回提案したデバイスの開発が進めば、ウイルスサイズのコンピュータの実現に近づく」とコメントしている。