東京工業大学(東工大)と富士通研究所(富士通研)は2月1日、72~100GHzの周波数範囲で高速に損失が少なく信号処理できるCMOS無線送受信チップとそのモジュール化技術を開発したと発表した。

同技術は、1月31日に米サンフランシスコで開催された「国際固体素子回路会議ISSCC 2016(IEEE International Solid-State Circuits Conference 2016)」にて発表された。

大容量データを無線伝送するためには、競合する無線アプリケーションが少ない30~300GHzの広帯域なミリ波帯の利用が適している。しかし、ミリ波帯は周波数が非常に高く、CMOS集積回路の動作限界に近いところで設計する必要があるため、設計の難易度が高く、広帯域な信号を高品質にミリ波帯へ周波数を変復調する送受信回路や、回路基板とアンテナを接続するインターフェース回路を低損失に実現することが難しい。

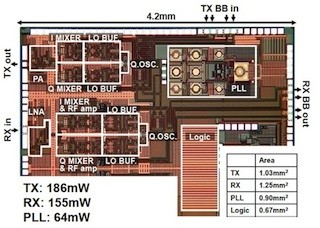

そこで両者は今回新たに、データ信号を2つに分けて、それぞれを異なる周波数帯へ変換してから混合することで、送受信回路を広帯域化・低損失化する技術を開発した。低帯域信号は72~82GHz、高帯域信号は89~99GHzのそれぞれ10GHz幅ごとに変復調を行うことにより、20GHz幅の超広帯域信号においても、低雑音で、入力と出力の電力比が一定となる範囲が従来の10GHz幅と同等となる変復調が可能になり、高品質な信号伝送を実現している。

また、ミリ波帯に周波数変換された信号を電波として送受信するための増幅器も合わせて開発。周波数によって部分的に増幅率が低下してしまう信号成分に対し、出力信号の振幅を入力側へフィードバックすることで増幅率を安定化させる回路技術を用いて設計し、72~100GHzの超広帯域の増幅器を実現した。

一方、半導体チップ上でミリ波帯に周波数変換された信号は、プリント基板上の信号線路を伝搬してアンテナへ供給されるが、アンテナは導波管という金属状の筒で形成されているため、プリント基板と導波管の間を超広帯域、かつ低損失に接続することが必要となる。今回、プリント基板上の配線パターンを工夫することで、超広帯域向けにインピーダンス整合させた導波管と基板の間のインターフェースを開発し、所望の周波数範囲で大幅に損失を低減することができた。

今回開発された技術を利用し、室内において10cmの距離を隔てて2台のモジュールを対向させてデータ伝送試験を実施したところ、導波管と基板の間の損失について10%以下を実現し、世界最高速となる毎秒56ギガビットのデータ伝送に成功したという。

同技術に加えて、信号を増幅して伝搬距離を伸ばすための高出力増幅器技術や、超広帯域信号を処理するベースバンド回路技術を組み合わせることで、屋外設置可能な無線装置の大容量化が可能となる。これにより、新規に光ファイバーを敷設することが困難な都市部や河川を挟んだ山間部などへも無線による大容量な基地局ネットワークを展開できることが期待される。

両者は、スマートフォンなどの基地局間通信向けの無線基幹回線をターゲットとして2020年ごろの実用化を目指すとしている。