東芝は2月21日、デジタル信号処理に代わる新たな信号処理方式として、デジタル信号を時間領域で表現する時間領域信号処理技術を開発したと発表した。また、同技術をNAND型フラッシュメモリの誤り訂正処理に用いられるLDPC復号回路に適用し、回路規模を38%縮小できることを実証したという。

詳細は2月17日より米国サンフランシスコで開催されている「ISSCC 2013(International Solid-State Circuits Conference:国際固体素子回路会議)」にて発表された。

現在、NAND型フラッシュメモリはプロセスの微細化などにより電荷を保持できなくなるといった影響から信頼性向上が求められており、その技術の1つとしてLDPC符号などの誤り訂正回路に注目が集まっているが、LDPC符号は復号回路の回路規模が大きいという課題があった。

これは、復号に従来の1か0かという情報だけではなく、1である確率と0である確率という情報を用いるため、回路で処理すべき情報量が多くなるためである。その問題を解決するために、0Vから1Vの間を連続的に1本の配線で表現できるアナログ回路を使う方式が提案されてきたが、アナログ信号とデジタル信号を相互変換する回路の電力・面積が大きくなることや、デジタル回路設計に用いられる自動設計ツールが利用できないため、チップ全体の面積や開発コストが大きくなるといった問題があり、製品適用には至っていなかった。

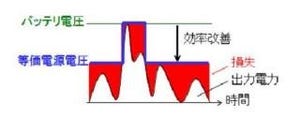

今回開発された時間領域信号処理は、LDPC復号回路で処理される情報を、デジタル回路のようなHigh/Lowといった2値の組み合わせや、アナログ回路のように電圧値で表現するのではなく、デジタル値がLowからHighに変わる時間を使って表現するもので、これにより、アナログ回路と同じように、一本の配線で確率を表現することができるようになるという。

また、時間というアナログ信号を扱うにもかかわらず、すべての回路部品はデジタル回路と共通で、従来から用いられているデジタル回路設計用の自動設計ツールを利用して開発できるほか、時間信号とデジタル信号を相互に変換する回路を小規模な回路で実現できるという。

なお、この時間領域信号処理を用いて、実際にNAND型フラッシュメモリの小規模なLDPC復号回路を試作したところ、デジタル回路で実装した場合に比べ回路規模を38%縮小できることを確認したと同社では説明している。