富士通研究所は、次世代の高性能サーバを実現するにあたり、サーバ内での高速・広帯域なデータ通信用の光インタコネクトに必要となる小型・低コストな光トランシーバ技術を開発したことを発表した。同成果は5月29日から米国サンディエゴで開催されている電子部品の実装技術に関する国際会議「ECTC2012(IEEE 62nd Electronic Components and Technology Conference)」で発表された。

近年、CPUの高性能化にともない、サーバのデータ処理能力が向上するとともに、1つのCPUに複数プロセスを集約させる仮想化技術も進展しており、CPU間や、CPUと周辺デバイス間でやりとりするデータは増加の一途をたどっている。このデータ増大の解決策として、すでにサーバ間を1chあたり10Gbps程度の転送速度で接続する光インタコネクトが適用されているが、次世代の高性能サーバ実現に向けて、さらに高速化した25Gbpsの転送速度への期待が高まっている。また、サーバ間だけでなく、転送速度の増大に伴い転送が難しくなっているサーバ内のボード間接続を、電気通信に代わって光インタコネクトを適用することで高速・広帯域なデータ通信を実現することも期待されるようになってきた。

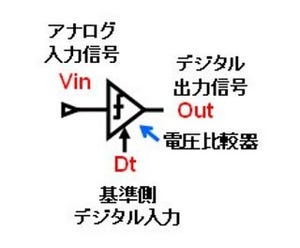

こうしたサーバ内での光インタコネクトを実現するためには、電気信号を光信号に変換する光トランシーバが必要になるが、従来の光トランシーバは転送速度が10~14Gbpsのため、次世代向けに期待されている転送速度25Gbpsを実現するためには光トランシーバそのものの速度向上が課題となっていた。また従来の光トランシーバはサイズが大きいためCPUなどのデバイスの直近に配置することが難しく、デバイスから光トランシーバまでの電気配線の距離が長くなるため、配線損失や配線間干渉により電気信号の品質が劣化し、高速化が難しいという課題もあった。

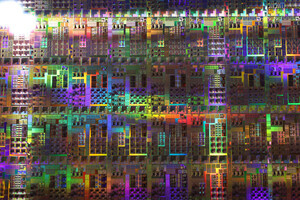

今回の研究では、サーバ内での高速・広帯域なデータ通信用の光インタコネクトに必要となる小型光トランシーバの実現に向け、電気(光)信号を光デバイスにより光(電気)信号に変換する光電変換部を開発した。

開発した技術は主に「高速回路技術」と「小型光結合技術」の2つの分けられる。高速回路技術としては、光デバイスを駆動するためのIC回路に、応答性能が劣る安価な光デバイスを用いても発光した光信号波形の立ち上がり立ち下りを急峻にする回路技術と、電気信号の波形を劣化させる多重反射を抑制する回路技術を搭載するにより高速化を実現した。これにより、1chあたりの転送速度を、従来の10~14Gbpsから25Gbpsまで高速化することに成功したという。

一方の小型光結合技術では、従来は、光電変換部と光ファイバとの間で光信号を効率よく伝達(光結合)するために、光結合部はレンズ部品と光コネクタを用いて構成されていたが、レンズ部品のサイズが大きく、コストが高いことが課題となっていた。

そのため、今回の研究では、フレキシブル基板に光デバイス、ICを実装して光電変換部を構成することで光トランシーバの小型化を図り、かつ安価なフィルム状のレンズシートを開発して、フレキシブル基板の裏面に積層する構造にすることで、この課題を解決した。この結果、光デバイスと光導波路間の光結合を高めることができるようになったことから、高速化による受信感度の低下を補うことができるようになったという。

実際にこれらの技術を用いて4ch×25Gbpsの光電変換部を試作したところ、22mm×9mm×0.86mm(搭載電子部品、光導波路を含む)のサイズで、従来のレンズ部品を搭載した光電変換部に比べ、レンズ部で10分の1以下、光電変換部で3分の1以下の薄型化を実現したという。

また、この薄さを活かして、試作した光電変換部を両面に搭載した光トランシーバを開発。送受信それぞれ8ch搭載で、47.8mm×16mm×21.6mmの小型化を実現しており、プリント基板上のCPUなどのデバイス近傍に小面積で実装することが可能となった。

なお、富士通研では、今回開発した技術を高性能サーバに適用するための研究・開発を進め、3年以内にサーバ内での光インタコネクトの実用化を目指すとするほか、今回開発した技術を広く情報機器・通信機器の高性能化に展開していく計画としている。