Alteraは10月11日(米国時間)、28nmプロセスとARMコアをベースとした新たなFPGAカテゴリとして「SoC FPGA」ファミリを発表した。

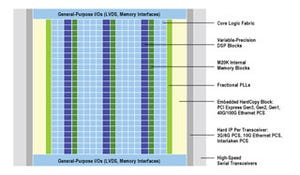

同ファミリは同社FPGAである「Cyclone V」および「Arria V」のFPGAファブリックと各コア800MHz駆動のデュアルコアARM Cortex-A9 MPCoreプロセッサ、NEONメディアプロセッシングエンジン、単精度/倍精度FPU、32KBのL1キャッシュ×2、共有されたL2キャッシュ512KBなどを搭載しているほか、DDR2/3とLPDDR2/3をサポートするハードIP化された専用メモリコントローラや最大3個のNOR/NAND型フラッシュメモリ用ECCコントローラ、PCI Express Gen2×4のハードIP(PCIe Gen2×8はソフトIPでサポート)、10Gbpsトランシーバ、USB2.0、CANなどを1チップに統合したもの。ARMの提供するエコシステムを継承しており、ARMコアプロセッサなどで用いられてきたソフトウェア開発ツール、デバッガ、OS、ミドルウェアおよびアプリケーションを活用することが可能だ。

Cortex-A9 MPCoreとFPGAは単にAXIバスで接続するのではなく、ACP(Accelerator Coherence Port)を活用した高スループットのデータパスにより相互接続されるため、プロセッサコアとFPGA間の外部I/Oが不要となり、システム電力の低減ならびにデータコヒーレンシを保ちながらの125Gbpsを超すピーク帯域幅を実現することが可能となっている。

|

|

|

Altera Vice President,Product and corporate marketingのVince Hu氏 |

Altera Vice President,Product and corporate marketingのVince Hu氏は、今回のARMとの協業について、「現在、圧倒的な数のカスタマがARMアーキテクチャを使っている。それらのエコシステムを継承することで、デザインツールに馴染みを有しつつ、我々がオファーするミドルウェアなども使うことが可能になる」と、ARMコアが組み込み分野で高い地位を占めつつあり、そこでのFPGA活用を狙ったことを説明しており、これにより従来のFPGA+CPUの2チップ構成に比べて、メモリデバイスなどの低減と、1.8W未満で4000DMIPSの性能と、可変精度DSPテクノロジーによる最大1600GMACS、300GFlopsの性能を実現することが可能だとしている。さらに、消費電力も従来の2チップシステム比で30%低減、ボードサイズも同最大55%の低減が可能だとしている。

また、併せて同社はSoC FPGA向け仮想開発環境「Virtual Target」も発表している。同ツールは、Synopsysとの協業により開発されたもので、「SoC開発のプロトタイピング手法を活用し、一切シミュレーションなどの経験がなくてもモデルを構築することを可能としたツール」(同)としている。

仮想プロトタイピングが可能となることで、実デバイスがなくてもソフトウェアを開発することが可能となる。同ツールと実デバイスは、バイナリ/レジスタレベルでの互換性が確保されており、バーチャルI/Oを活用したPCベースでの開発を行うことが可能なほか、拡張オプションである「FPGA-in-the-loop」を用いることで、ハードウェア化されたプロセッサシステムとカスタマ自身がデザインしたFPGAベースIPの両方をターゲットとしたソフトの開発が可能となる。

なお、同ツールについて同社では「既存のプロトタイピング用ツールと競合する用意がある」としており、低価格でのライセンス提供を行っていく予定。具体的な価格は非公開だが、少なくとも年間契約で1つのデザインチームの複数のエンジニアが共有して利用することが可能なライセンス形態での提供となるとしている。すでにLinuxサポート版の受注受付は開始されており、VxWorksサポート版を2011年内、FPGA-in-the-loopの拡張を2012年初頭から、それぞれ対応する予定としているほか、他のメジャーな組み込みOSに対しても、今後サポートを行っていく計画があるとしている。