東京大学大学院工学系研究科の鳥海明教授を中心とする研究チームは、電子、正孔ともに世界最高クラスの移動度を持つGeを用いた絶縁ゲート型電界効果トランジスタの開発に成功したことを明らかにした。12月6日から8日かけて米国サンフランシスコで開催されていた半導体デバイスの国際学会「IEDM 2010」において発表された。

Siを用いた半導体プロセスの微細化が進んだ結果、トランジスタのゲート長は50nmを切るところまで到達したが、その結果、さらなる性能向上にはさまざまな課題が生じており、Siという材料そのものの見直しも検討されている。また、グリーン化という観点から、半導体デバイスにもさらなる低消費電力化が求められており、そうした課題に対応するため次世代トランジスタ材料にも、以下の3点が要求事項として掲げられている。

- 集積化を前提にCMOS構造をコンパクトに実現できること

- 電子・正孔ともに移動度がSiに比べて十分に高いこと

- サブスレッショルド電流を十分に抑えたトランジスタを実現できること

新材料を用いた場合において、それにより従来Siで達成していた利点を失うのであれば総合的には性能を落とすことになりかねないという懸念がある。また、電子・正孔をそれぞれ独立に異なる材料で移動度を向上させる手法では、現実的に集積回路を作製する観点から集積化の実現が難しいということが考えられている。

こうした状況を鑑み、同研究グループではSiに代わる材料としてGeに着目、電界効果トランジスタにおける絶縁膜との界面の理解と制御の研究を進めてきており、2010年6月の「VLSIシンポジウム」において、Geについて今まで不可能とされてきた電子の移動度に関しての研究成果を披露するなどの活動を行ってきた。

今回、研究チームでは、Geを用いた電界効果トランジスタの高性能化に対する指針を構築し、それを実証する研究を行った。Ge基板上の絶縁膜二酸化ゲルマニウム(GeO2)とその界面の安定化に関しては、すでに高圧酸化という手法を用いることによって一酸化ゲルマニウム(GeO)の発生を熱力学的に抑え、良好なゲートスタック構造を実現することに成功しているが、同手法が界面に対しても最適な条件であるということは保証されていなかった。今回、その部分に焦点をあてて考えることで、界面特性の向上を図り、これにより上記要求項目の2と3を改善することを目指したという。

界面のGeOに関する平衡蒸気圧を熱力学的に考えると、温度を決めたならばGeOの平衡蒸気圧はGibbsの相律から一意的に決まる。つまり比較的高温で高圧酸化を施すことにより、GeO2膜の膜質は改善されるが、界面ではまさにその温度によって決まるGeOの生成が起きることになる。これは本質的なことであるため克服することは不可能と思われていたが、研究チームでは2つの方法を用いることで乗り越えたとする。

1点目は、酸素雰囲気下での低温熱処理。高圧酸化によって形成された良好なGeO2膜質を損なわずに界面におけるGeOの平衡蒸気圧を下げるために、高圧酸化の温度よりも低温で酸素熱処理を行うわけだが、あまりに低温であると現実的な時間で処理できないため、この温度と時間をうまく探し出せるかがポイントになる。この課題に対して、Ge表面かGeOの脱離がおよそ430℃辺りから始まるという実験結果をもとに、酸素アニール温度を400℃と設定した。

2点目は、規則配列した結晶中をある特定方向で切ったときに現れた面を示す「面方位」に対する選択。研究チームでは、同じ膜厚のGeO2がGe基板上に堆積される時にGeOの脱離が始まる温度が面方位によって異なるという事実を発見。具体的には、面方位を(100)、(110)、(111)面で比較した時に(111)面がGeOの脱離に対して最も安定であることが実験でも確かめられた。

このことは、(111)面上ではGeO脱離が起きにくく他の面に比べて安定になりやすいことを示している。電子にとって有効質量の観点から(111)面が優位であるということ(有効質量の面方位依存性)は2010年のVLSIシンポジウムでも議論したものであるが、界面の構造的安定性からも優位であることを意味していると研究チームでは説明している。

これらの知見をもとに、p型(111)面Ge基板上にNチャネル型絶縁ゲート型電界効果トランジスタを、また、n型(100)Ge基板上にPチャネル絶縁ゲート型電界効果トランジスタを作製した。

また、それぞれの面上にMOSキャパシタを作製し界面欠陥密度を評価した。この際、Pチャネル電界効果トランジスタでは有効質量の観点から(111)面の優位性はないので(100)面を使ったという。

MOSキャパシタにおける容量-電圧特性の周波数依存性の詳細評価から、フォーミングガスアニールを施していないにも関わらず、バンド端側における界面欠陥密度が減少していることが見て取れた。

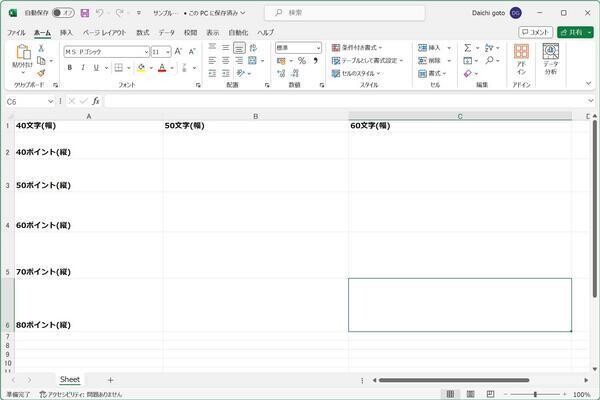

|

|

|

トランジスタの基本になるMOS型キャパシタの容量-電圧特性から求めたGe基板における欠陥界面準位のスペクトル。各種プロセス、ゲートスタック構造の結果を示しており、ミッドギャップ付近で1011eV-1cm-2以下が実現されている。今回の特性は特にバンドギャップ端に向かって界面準位密度が改善されていることが移動度改善に寄与している |

さらに、電界効果トランジスタ性能としては、電子移動度が約1920(cm2/Vsec)、正孔移動度が725(cm2/Vsec)の世界最高クラスの電子移動度、正孔移動度を達成した。これはSiの電子移動度の約2.5倍、正孔移動度の約3.5倍にあたり、現在、各所で研究開発が進められている歪みSi(sSi)FETにおける移動度向上を超えるものであるほか、電子移動度に関しても、2010年6月に同研究グループが発表した結果(1480cm2/Vsec)を超えるものとなっている。

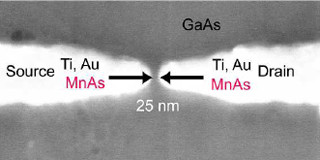

|

|

|

室温における電子・正孔の移動度の界面におけるキャリア面密度依存性。各種プロセス、ゲートスタック構造の場合について示しており、電子と正孔の移動度に関して、最も高い値はこれまでに報告されている値の中で電子・正孔ともに世界最高クラスの値となった |

加えて、界面が改善したことにより、移動度の温度依存性はSi MOSFETと同様な振る舞い(温度低下とともに移動度が上昇する)を示すこともでき、半導体固有の性質をGeでも実現できたことを示している。

サブスレッショルド・スロープも小さく、界面特性が向上していることも判明したほか、界面特性が向上したことにより、しきい値以下の電流を示す特性(サブスレッショルドスウィング)をSi並みに改善することができた。実際、このことも従来のGe電界効果トランジスタでは問題となっており、同特性が改善されないと低電圧動作は難しかった。同結果は、現実的に低電圧動作CMOSを考えるうえで移動度と同程度に重要な結果と言えると研究チームでは説明している。

なお、研究チームでは、さらなるプロセスの最適化あるいはGeに対する歪み技術の適用により、今回の結果を超える高性能化が期待できるとする。ただし、微細化に向けてはゲート絶縁膜をさらに薄膜化する必要があり、高誘電率絶縁膜の適用が鍵になるとするほか、トランジスタの高性能化に対しては、ソースとドレイン部における不純物の制御、接触抵抗の低抵抗化も重要で、これらに関しても抜本的な改善を図るには界面の理解と制御が鍵となることから、積極的に今後も研究を進めていく予定としている。