富士通研究所は、次世代不揮発性メモリの1つであるスピン注入型MRAMについて、MTJ素子の磁性体の順序を従来と逆転させることで、従来比60%の小型化と、高集積化が可能なメモリセル回路を開発した。同技術の詳細は、2010年6月15~17日に米国ハワイ州で開催される半導体デバイスに関する国際会議「VLSI技術シンポジウム(2010 Symposium on VLSI Technology)」にて発表された。

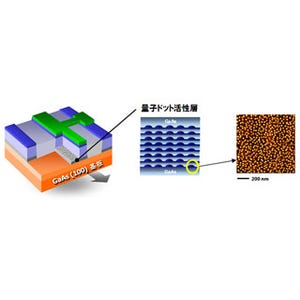

スピン注入型MRAMは、磁性材料に電流を流すことで磁化の方向が反転する現象を利用した記憶素子。電流を流した際に磁性材料の磁化の方向が平行になったり逆になったりすることで、素子が低抵抗と高抵抗になる現象を、デジタル情報の"0"と"1"として対応させることで、不揮発性の磁気メモリとして利用している。

しかし、スピン注入型MRAMで使われているMTJ素子は微細化が可能なのに対し、それに付随するセル選択トランジスタの小型化が課題となっていた。

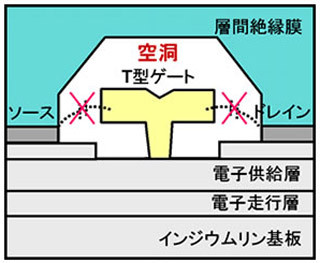

スピン注入型MRAMのメモリセル回路は、どのMTJ素子に記録を書き込む(読み込む)かを選択するスイッチの役割をするセル選択トランジスタと、MTJ素子を接続した回路で、従来のメモリセル回路では、スピン注入型MRAMのMTJ素子に対して高抵抗("1")の書き込み時には可変抵抗によって電圧が低下し、可変抵抗の影響を受けない低抵抗("0")の書き込み時よりも、大きな書き込み電流が必要になっていた。つまり、セル選択トランジスタの電流駆動能力の低い方で、大きな電流が必要となる高抵抗("1")の書き込みをしなくてはならず、電流駆動能力が低い時でも、大きな書き込み電流を確保するために、セル選択トランジスタのサイズを大きくする必要があった。

今回富士通研では、MTJ素子の磁性体の順序を逆転させ、従来と異なるピン層、絶縁膜、フリー層からなるトップピン構造のMTJ素子を開発したが、このままではトップピン構造のMTJ素子の絶縁層と下部電極の距離が近くなるため、加工の際にショート不良を生じやすくなるため、対策として、バッファ層を挿入して絶縁層と下部電極の距離を離した。これにより、セル選択トランジスタの電流駆動能力が低い方向と、低抵抗("0")な書き込みの出力方向が同じになり、より小さいサイズのセル選択トランジスタでも機能することが可能となったという。

結果としてメモリセル回路面積は従来の60%に小型化でき、スピン注入型MRAMの集積度を高めることが可能となり、NOR型フラッシュマイコンよりも、小型で、高速にアプリケーションを動かすことができる、高性能なスピン注入型MRAM内蔵マイコンの実用化の可能性が広がったこととなった。

なお、富士通研では、今後は、スピン注入型MTJ素子の微細加工技術の開発など、スピン注入型MRAMの実用化に向けた研究開発を推進していく計画としている。